Designing an ARM Based SoC: How to Meet Your Power Budget

ARM IP and ARM processor usage is pervasive across multiple segments of the electronics industry. As shown in Figure 1, each of these market segments have unique design challenges and analysis drivers. For example, a SoC targeting a mobile hand...

ARM IP and ARM processor usage is pervasive across multiple segments of the electronics industry. As shown in Figure 1, each of these market segments have unique design challenges and analysis drivers. For example, a SoC targeting a mobile handset or tablet will require high-performance, while still meeting the overall power budget. Memory and I/O IP on the other hand, must be designed for immunity to noise that is coupled via the power grid routing, the package, or the substrate. SoCs targeting automotive or medical industries must meet high reliability standards and minimize their electromagnetic interface (EMI) signature.

Figure 1: Market segment specific design considerations for an ARM IP based SoC.

Using a power and noise budgeting methodology

Given the unrealistic time-to-market (TTM) requirements for these products, and the aggressive power target, performance and reliability requirements, it is desirable to design these SoCs up-front in order to eliminate such concerns. However, "over-design" is not an option because it only adds to the cost and does not necessarily address design needs. Meeting these stringent market and engineering constraints requires a low-power design methodology that addresses both the power and noise budget. Power budgeting enables a design to meet system power requirements by analyzing, reducing, and tracking power through the entire design cycle. Noise budgeting on the other hand, predicts the fluctuations in the power supply network from the flow of current in the circuit. This allows design teams to identify different ways to minimize the impact of power noise and current flow on timing, functionality and reliability. Figure 2 illustrates a methodology where the power budgeting effort is started early in the design flow to help identify 'power bugs' and improve the overall power efficiency of the design, whether it is in the clock tree, the data path, or in the memory sub-systems. As the physical design kicks in, the noise budget analysis helps identify potential fallouts on power noise from the low-power design techniques that are employed. For example, power gating, commonly used to reduce leakage or standby power, can severely impact a design if the power gates are turned on improperly. A large rush-current' condition can be generated that will result in the collapse of the supply voltage, degrading its performance and/or its functionality.

Figure 2: A unified low-power analysis flow targeting both power and noise budgeting requirements.

Apache and ARM partnership: IP collaboration and examples

Apache collaborates with ARM on multiple levels, including A.) the availability of Apache's Power Library (APL) for ARM Artisan® standard cell libraries and Apache Virtual Modeling (AVM) for Artisan memories; B.) the use of Apache products for designing and validating ARM processor cores and IP; and C.) the development of advanced analysis methodologies targeting ultra-low-power circuits designed in 28nm or below technology nodes.

The availability of Apache Power Library views for standard cell and memory libraries enables ARM customers to run RedHawk™ analyses on their designs, without any additional library characterization efforts, while still benefitting from RedHawk's silicon validated accuracy. In addition, physical IP design teams working on advanced memory and I/O designs use Totem™ to simulate and analyze their designs for power noise and reliability; ensuring robust designs ready for advanced technology nodes. Collaboration continues on the use of advanced products such as PathFinder™ to validate ARM designs for ESD robustness.

Another area of collaboration is in the use of Apache technologies such as PowerArtist™ and RedHawk for the design, analysis, and validation of ARM processor cores and IP. PowerArtist is part of a collaboration aimed at analyzing RTL stage power, identifying potential power efficiency gains, and performing power regressions to track power through the design cycle of the processor. Cooperation continues in creating flows that will result in the generation of advanced RTL power models that help in early power grid and package design prototyping, and in improving the accuracy of the sign-off power noise analysis. ARM engineering uses RedHawk to analyze advanced low-power designs, covering static IR, power EM, dynamic voltage drop, and rush current analysis. RedHawk simulation also considers the impact of the package on the performance of the ARM designs, while Apache Chip Power Models (CPM™) are created and delivered to package design partners who use the CPM to optimize and validate their designs.

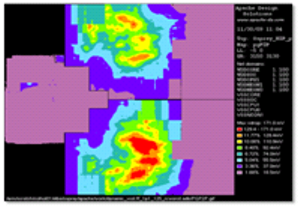

An example of ARM and Apache collaboration is seen in Figure 3, where an ARM design team used RedHawk to validate and improve the hard-macro implementation of the ARM Cortex-A9 design on the chip and at the associated die-package interface.

Figure 3: Dynamic voltage drop analysis on a dual Cortex-A9.

Guest Partner Blogger: Aveek Sarkar of Apache Design Solutions, now Apache Design, Inc., a wholly-owned subsidiary of ANSYS, joined the company as a Senior Applications Engineer in 2003. Since then he has taken on different roles and responsibilities inside Apache including director of product engineering. Prior to joining Apache, Mr. Sarkar worked for several years in Sun Microsystems on several generations of UltraSparc processors. Prior to Sun Microsystems, Mr. Sarkar held engineering positions at Cadence Design Systems and National Semiconductor. Mr. Sarkar holds a B.Tech from the Indian Institute of Technology, Kanpur, a MSEE from Oregon State University, and a MBA from Santa Clara University.

Aveek Sarkar of Apache Design Solutions, now Apache Design, Inc., a wholly-owned subsidiary of ANSYS, joined the company as a Senior Applications Engineer in 2003. Since then he has taken on different roles and responsibilities inside Apache including director of product engineering. Prior to joining Apache, Mr. Sarkar worked for several years in Sun Microsystems on several generations of UltraSparc processors. Prior to Sun Microsystems, Mr. Sarkar held engineering positions at Cadence Design Systems and National Semiconductor. Mr. Sarkar holds a B.Tech from the Indian Institute of Technology, Kanpur, a MSEE from Oregon State University, and a MBA from Santa Clara University.

Re-use is only permitted for informational and non-commercial or personal use only.