Five things you didn't know about the ARM® Cortex®-A15 Processor

By now, everyone knows that the ARM Cortex-A15 processor is ARM’s highest performance v7a ARM core to date. The Cortex-A15, along with the other ARM-based cores, are helping tablets surge a projected 53.4% this year, and has been part of some f...

By now, everyone knows that the ARM Cortex-A15 processor is ARM’s highest performance v7a ARM core to date. The Cortex-A15, along with the other ARM-based cores, are helping tablets surge a projected 53.4% this year, and has been part of some flagship phones that are setting milestones on performance and capability. But, I bet that there are still 5 things you didn’t know about this high performance CPU:

1. The Cortex-A15 powers the Samsung Chromebook - the best-selling Laptop on Amazon.com and has held that position since the laptop was released last year!

There has been incredible demand for a small, light mobile device in a laptop form factor that runs an operating system similar to those found on mobile handsets, but with all-day battery life and the familiar keyboard for data entry. Many people originally expected this to be a fad product, but the strong shipment data has shown that they underestimated the performance of the Cortex-A15 and just how good the user experience can be. The fact that it has endured as the best-selling laptop shows that consumers not just expect ARM to power their smartphones, they also want to meet all their computing needs with products based on power-efficient ARM technology.

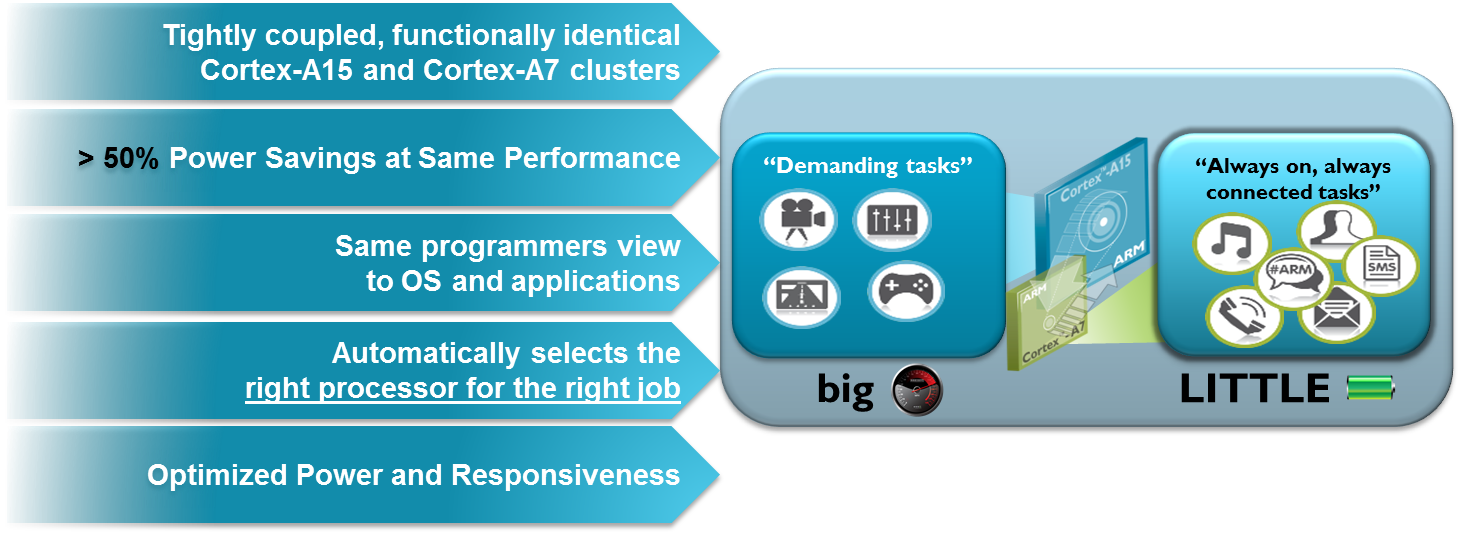

2. The Cortex-A15 is the first “big” core within ARM’s big.LITTLE family of technology products.

Our technology allows you to optimize both power and performance in many applications, not just mobile devices. Today, Cortex-A15 is the performance leader in shipping smartphones, providing not just the performance you expect, but has the ability to extend your battery life by shifting lower-demanding threads to the Cortex-A7 core.

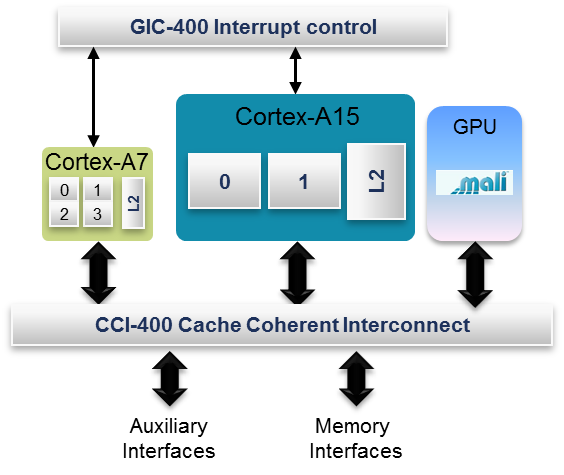

A big.LITTLE configuration featuring Cortex-A15, Cortex-A7, CCI-400, GIC-400

I expect that mobile configurations using the Cortex-A15 and Cortex-A7 processors that are tied together using the CCI-400 Cache Coherent Interconnect will deliver over twice the performance of last year’s high end phones – with the same or better battery life!

It is pretty easy to visualize how a system that uses big.LITTLE can save on battery life. One analogy can be a hybrid powertrain for a car. The “big” gasoline or diesel engine is like the ‘big’ core – it provides the serious horsepower when needed. But, the “LITTLE” electric motors provide the base performance of many cars up to 30-40MPH. When you need serious performance, assign a thread or series of threads to the Cortex-A15 cluster and users can experience performance of almost three times what a system based on the Cortex-A7 alone can do. Most of the time you are using your smartphone or tablet, you don’t need peak performance, so why spend the extra milliWatts? big.LITTLE Software automatically divides work between the high performance Cortex-A15 cores and the highly efficient Cortex-A7.

Additionally, what you may not realize is that by using advanced big.LITTLE techniques, you can achieve even greater levels of performance than a Cortex-A15 can do alone:

- The first reason is that the LITTLE cores open up additional performance enhancing power management and task allocation policies. As one example, the software will move low-priority background threads to the little cores. All of this means that background work that otherwise would cause interruptions to the larger core are assigned to the LITTLE cores. This concept is called task isolation - devoting the full capacity of a Cortex-A15 CPU to execute the most demanding high-performance threads allows it to dedicate its full capacity to the dominant threads in a system. I only wish I could similarly focus my own work effort, without the interruption of emails, texts, Skype messages, and phone calls!

- The second reason is that system builders can also optimize the implementation for performance – choosing a higher frequency target means that the top speed of the processor can be higher than what you might otherwise choose without big.LITTLE. This allows a designer to design a system where the right task is assigned to the right processor.

3. The Cortex-A15 IP is extremely flexible and can be configured to many different markets and form factors. The only limit is your imagination! Some of the announced products include:

- Smartphones like the big.LITTLE-powered Samsung Galaxy S4 (in select markets) which features a quad-Cortex-A15 and a quad-core Cortex-A7

- Tablets like the Samsung Galaxy Note 4

- Laptops like Samsung’s best-selling Chromebook and HP’s Chromebook 11. Both are powered by a dual Cortex-A15 processor

- Microcomputers like the Odroid-XU which features a quad core Cortex-A15 and quad core Cortex-A7 big.LITTLE processor

At the other end of this spectrum, we have the Cortex-A15 expanding on the beachhead started by the Cortex-A9 in server and networking markets. One of the first Cortex-A15 server platforms that we see is based on the EnergyCore® ECX-2000 family from Calxeda. In the networking space, LSI is successfully deploying a 16-core Cortex-A15 SoC. LSI’s Axxia platform is now providing significantly more scalability and flexibility to wireless infrastructure markets.

As they say, “but wait, there’s more!” You can expect additional product announcements throughout the rest of 2013 and through 2014.

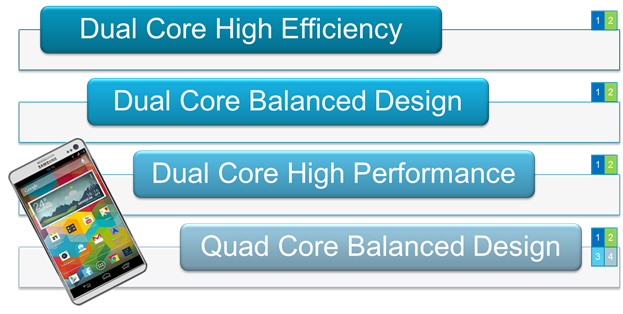

4. An important feature is that the IP can be tuned to hit very different power and performance targets. This is important when considering how to answer “how much power does this processor draw?” While productizing the Cortex-A15, there are many different implementation options that can be considered. You can vary the core count, the L2 size, the library set (a fab typically offers more than one set of libraries within a process, so you can tweak your design for power, performance, or a balance of the two), the transistor threshold voltages, and so on. ARM provides POP (processor optimization package) solutions which get you best set of results that are focused on power or performance or both. These solutions help reduce your time to market.

We offer 4 different solutions through our POP program:

Additionally, ARM has two hard macros that are fully signed off and ready to be dropped into your SoC design. These include a dual core targeted for the mobile space and a quad core targeted for the server and networking space:

Additionally, ARM has two hard macros that are fully signed off and ready to be dropped into your SoC design. These include a dual core targeted for the mobile space and a quad core targeted for the server and networking space:

Available now, these macros give you the ability to drop in a hardened processing solution and let you focus on bringing value to the rest of the system.

The Cortex-A15 is viewed as such an important IP block that our major EDA vendors have invested in reference implementations that help get you closer to a complete design with less effort and time. These implementations complement our POP and hard macro offerings with specific performance and power targets designed to excel in specific markets and can help get you closer to a completed design with less effort and time required. Combined with ARM’s POP and Hard Macro offerings, the Reference Implementations round out a full range of offerings that enable SoC designers to achieve specific targets for performance, power, and area.

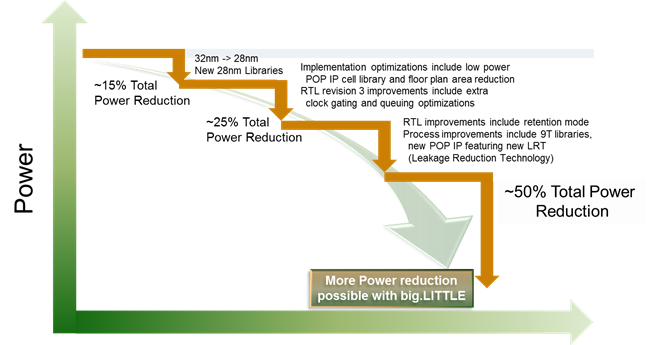

5. The Cortex-A15 IP is periodically refreshed with improvements that help our partners succeed in their respective businesses. As you can see in this figure, efficiency improvements have been implemented in an ongoing basis yielding an overall power reduction of about 50% from the initial implementations.

Power Reductions over time for the Cortex-A15

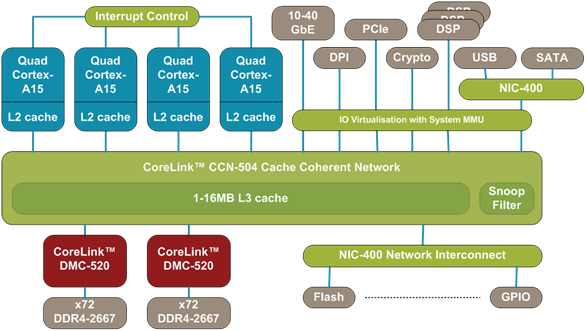

Another improvement is the addition of connectivity to the high performance CoreLink CCN-504 Cache Coherent Network interconnect.

A Block Diagram of a 16-core Cortex-A15 SoC

The Cortex-A15 can be paired with the CoreLink CCN-504 Cache Coherent Networking interconnect to create a 16 core system on a chip solution. LSI is the first to bring this to market. The Cortex-A15 will enable our partners to bring ARM-class efficiency to server and networking markets at a compelling performance level. Finally, OEMs will be able to offer designs based on ARM’s high efficiency processor cores to networking and server customers where they can optimize their workloads with ARM processors.

In summary, the five attributes described here are a few of the more interesting features of the Cortex-A15 processor. Consumers in many markets are about to get to know the Cortex-A15 a lot better – it will be “under the hood” in many of the most compelling mobile and consumer products shipping in 2013 and 2014. Beyond its most visible deployment in sexy mobile devices, the Cortex-A15 will be hard at work behind the scenes powering new networking and server products that are accelerating the transition of enterprise infrastructure to low power ARM technology.

I hope that you learned something new with these 5 things about the Cortex-A15. I am excited to see this IP brought to life in so many different markets and look forward to seeing what YOU can do with it!

Re-use is only permitted for informational and non-commercial or personal use only.