Arm Cortex-A720 and Cortex-A520 CPUs extend Armv9 benefits to all consumer device markets

This blog provides details about the new Arm Cortex-A720 and Cortex-A520 CPUs that bring Armv9 features and benefits across every tier of consumer device.

In the Arm CPU cluster, the Cortex-A700 and Cortex-A500 series CPUs perform vital functions to enable the experiences that users enjoy on their consumer devices. The Cortex-A700 series of CPUs is a hugely successful product range used across a broad range of application and markets: set-top boxes (STBs) and DTVs, smartwatch and XR wearables, smartphones and laptops. Acting as the ‘workhorse’ in the cluster, Cortex-A700 CPUs push high performance in a constrained power envelope. Meanwhile, Cortex-A500 CPUs deliver the best energy and power efficiency in the smallest silicon footprint.

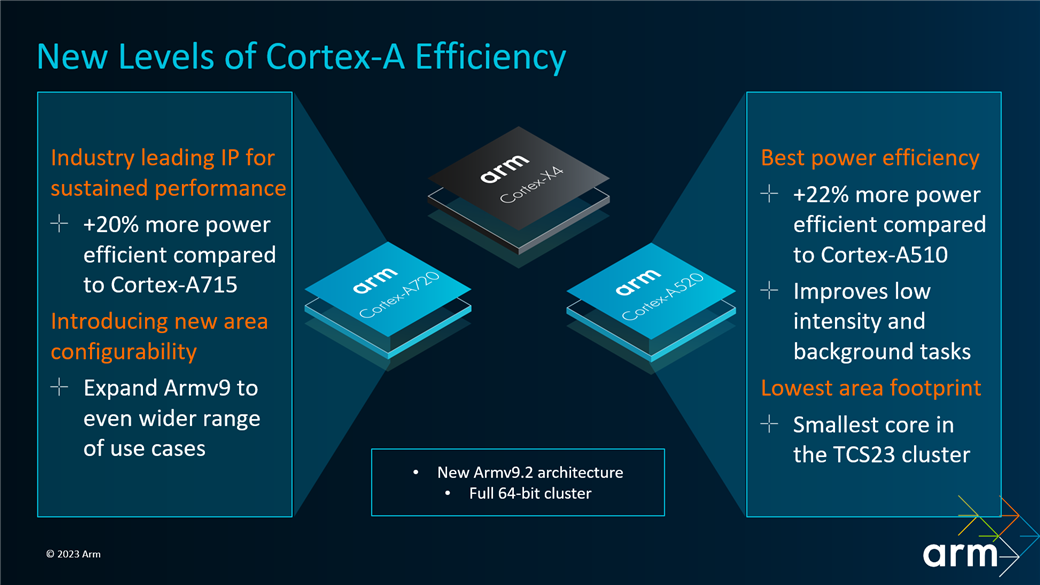

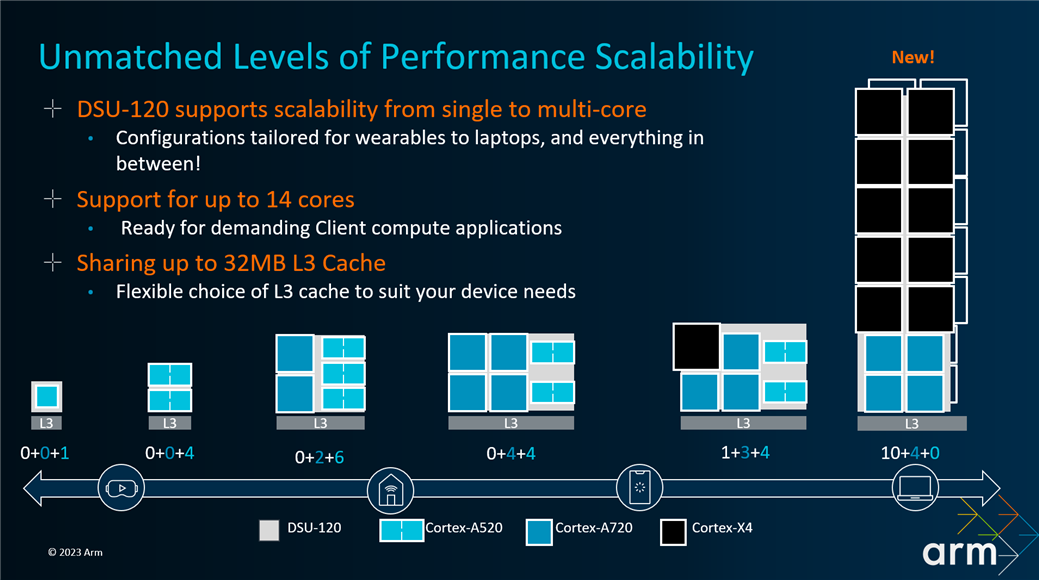

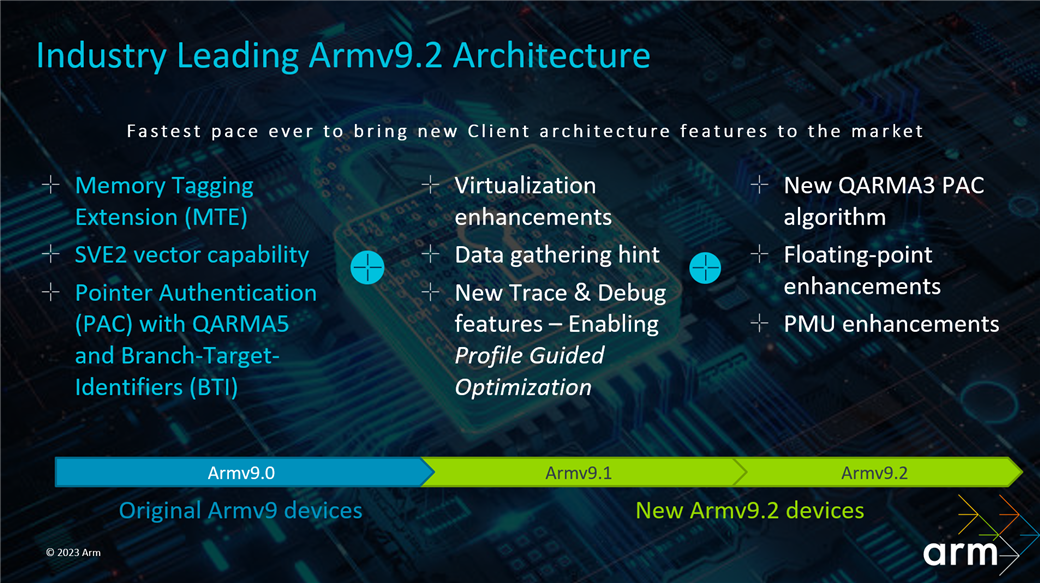

This year we are delighted to launch two new products to add to both product series: the Cortex-A720 and Cortex-A520 CPUs. Both products, which are built on the new Armv9.2 architecture, enable Armv9 computing capabilities across all tiers of consumer devices. Integrating both CPUs with the new DynamIQ Shared Unit, the DSU-120, provides intelligent power-saving features, enhanced PPA and even greater scalability. This enables the CPU clusters featuring Cortex-A720 and Cortex-A520 to reach high levels of performance, efficiency, and scalability.

Even in the lower tiers of consumer devices (mainstream and entry), there is a greater demand for more advanced computing capabilities for the seamless experiences that users now expect. As the hub of the smart home, STBs and DTVs need greater performance for streaming services, as well as the ability to secure data through more advanced security features. Mid-range and entry-level smartphones are now seeing the rapid adoption of 5G, providing advanced connectivity capabilities for users to enjoy their favorite applications ‘on-the-go’. Developers also expect that their applications can be written and then run on any mobile device, not just premium, and flagship smartphones.

Against this backdrop of emerging use cases and increasing user demands across all consumer device markets, we are providing improvements in performance, efficiency, and features through Cortex-A720 and Cortex-A520. This gives our partners the flexibility to build the right ‘big.LITTLE’ CPU clusters for their portfolio of devices.

Cortex-A720: Industry leading sustained premium performance

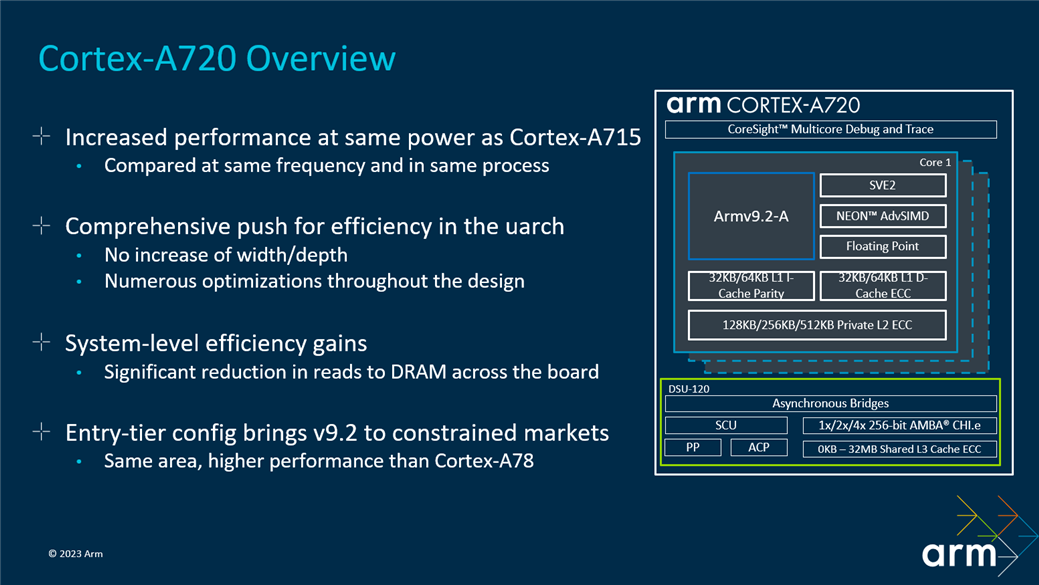

Cortex-A720 is the industry-leading IP for sustained premium performance, delivering 20 percent more power efficiency compared to the previous generation Arm Cortex-A715¹. Optimized to benefit full system power and performance with the latest microarchitecture improvements, Cortex-A720 is designed to answer demands for more performance and longer battery life within the form factor and thermal constraints of modern consumer devices. This delivers more sustained performance for faster, longer gameplay and untethered creativity. The microarchitecture improvements and optimizations include the adoption of the latest process nodes that improve on-device sustained performance.

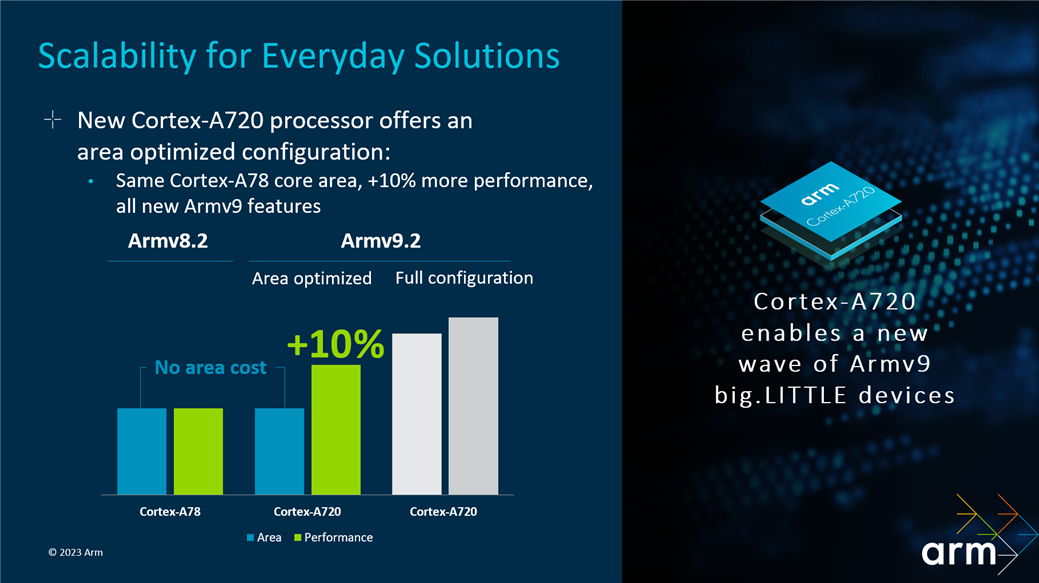

These levels of performance and efficiency are not just reserved for premium consumer device markets. We have ensured that the improvements are applicable across all solutions for consumer devices, even those more constrained by cost and area. Cortex-A720 can be configured at implementation time to match the area footprint of the Arm Cortex-A78, but provides 10 percent more performance². This is alongside greater efficiency and the latest Armv9.2 features for security and machine learning (ML). This new area optimized configuration of Cortex-A720 expands Armv9 to an even wider range of use cases and devices, particularly lower-end markets. Also, the compatibility with the new DSU-120 ensures the Cortex-A720 can be used in big.LITTLE clusters with Cortex-A520 to address multiple consumer device tiers, including mainstream mobile, STBs, DTVs, and wearables.

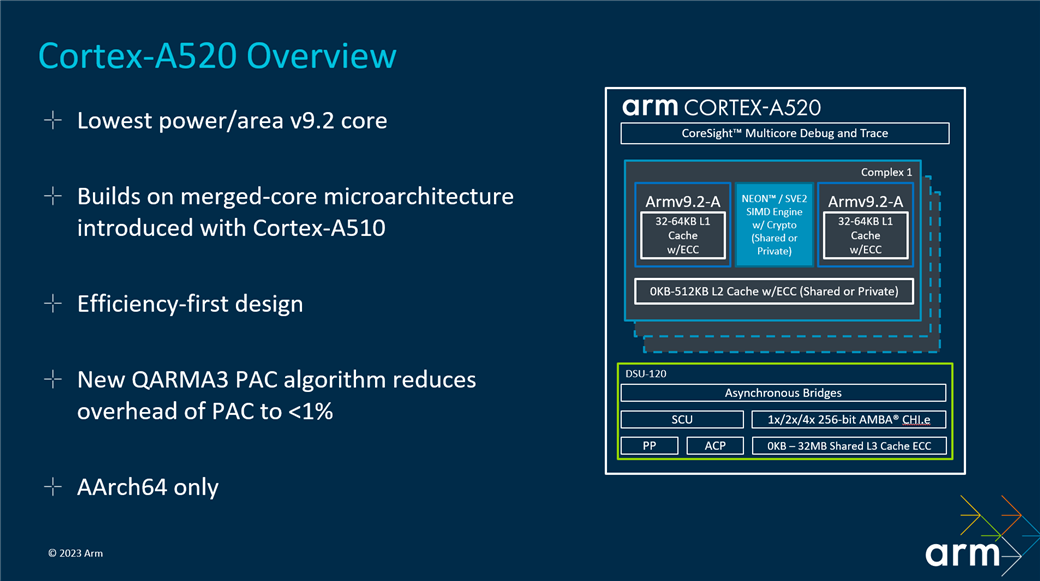

Cortex-A520: The best power efficiency design

Cortex-A520, our latest LITTLE core, has an unrelenting focus on delivering the very best power efficiency in the smallest silicon footprint, with improvements of 22 percent over the previous generation Cortex-A510³. This reduces the computing power required for low intensity background workloads to improve battery life on consumer devices for longer untethered experiences. Building on the merged-core architecture introduced two years ago with Cortex-A510, these high efficiency improvements are made possible through additional microarchitecture-level changes, particularly around data prefetching and branch prediction. While Cortex-A520 is an ‘efficiency-first’ design, it provides up to 8 percent more performance compared to Cortex-A510⁴.

Cortex-A520: 64-bit only and advanced Armv9 security and ML features

Cortex-A520 is the first true 64-bit only Arm LITTLE CPU, with 64-bit only mobile devices already arriving on the market and more expected to follow. Nearly all the mobile app stores worldwide have been requiring 64-bit support for at least the past year, with the app ecosystem ready for 64-bit only devices.

Being 64-bit only helps our partners deliver greater computing performance and more security and ML features, while improving the app development process. On computing performance, the 64-bit instruction set delivers performance gains of up to 20 percent⁵ for faster app loading times and better, more responsive user experiences. This helps to meet the insatiable demand for more computing across various workloads, particularly for AI and AAA gaming.

A wide majority of today’s Android mobile devices deploy a version of the OS (version 5.0 and above) capable of simultaneously supporting both 64-bit and 32-bit Android runtimes. However, this comes at a cost of additional memory, development, and testing. Prioritizing 64-bit application development as part of this transition to 64-bit only mobile devices means reduced complexity, lower development and testing costs, and an improved time-to-market. It also allows the Android ecosystem to focus on supporting newer features and technologies, with the advanced performance and robustness not possible in the 32-bit architecture.

The 64-bit architecture offers enhanced security for devices through Armv9 features, which include Pointer Authentication (PAC), Branch Target Identification (BTI) and Memory Tagging Extension (MTE). These features remove up to 95 percent of certain classes of vulnerabilities, including memory safety violations that account for the majority of all serious security bugs. And we continue to make security enhancements through the Armv9.2 architecture. The new QARMA3 PAC algorithm introduced this year reduces the overhead of PAC to less than one percent for LITTLE cores.

Growth in MTE enablement

MTE is available across all tiers of consumer devices, with its adoption continuing through Cortex-A720 and Cortex-A520. MTE remains hugely beneficial to the Arm ecosystem because it allows developers to detect and avoid memory safety vulnerabilities before and after deployment. This speeds up the application debugging and development process. Multiple Arm partners who are committed to tackling memory safety bugs in the software ecosystem have already built and enabled the MTE feature across their chipsets. For example, Honor recently announced that its MTE enabled MagicOS 6.x and Magic OS 7 devices will be available to developers through its Honor SkyNet and in future DiagnosisKit tools. This work is already having a positive impact, with Kuaishou, one of the world’s largest short video platform providers, using MTE to transform its development process. This is bringing more secure, safer experiences to its 360 million daily average users.

Improvements for all tiers of consumer devices

Cortex-A720, Cortex-A520, and DSU-120 offer comprehensive features and benefits for all tiers of consumer devices. Cortex-A720 pushes sustained performance for better, longer user experiences, while its area optimized configuration provides new opportunities for Armv9 performance and features on lower-tier devices. Cortex-A520 delivers the highest levels of power efficiency to expand the battery life of consumer devices, while the adoption of Armv9 security features brings security and software benefits at every touchpoint of the Arm ecosystem. DSU-120 offers high scalability and flexibility, intelligent power modes and enhanced PPA, tailored to fit all consumer devices, from wearables, DTVs and STBs, smartphones and beyond. Thanks to Cortex-A720, Cortex-A520 and DSU-120, Armv9 benefits, features and performance and efficiency improvements are available at every tier of device. It is not just architecture for the higher-end, Armv9 is truly for all markets.

Footnotes

¹ Comparing Arm Cortex-A720 SPECint_base2006 power efficiency. Cortex-A720 using 32KB L1, 512KB L2, 8MB L3 and Cortex-A715 using 32KB L1, 512KB L2, 8MB L3 (iso-process, iso-frequency).

² Comparing Arm Cortex-A720 "area optimized" SPECint_base2006 performance and Cortex-A78. Cortex-A720 using 32KB L1, 128KB L2, 2MB L3 and Cortex-A78 using 32KB L1, 256KB L2, 2MB L3 (iso-process, iso-frequency).

³ Comparing Arm Cortex-A520 SPECint_base2006 power efficiency. Cortex-A520 using 32KB L1, 256KB L2 (shared w/ 2 CPUs), 4MB L3 and Cortex-A510 (2022) using 32KB L1, 256KB L2(shared w/ 2 CPUs), 4MB L3 (iso-process, iso-frequency).

⁴ Comparing Arm Cortex-A520 SPECint_base2006 performance. Cortex-A520 using 32KB L1, 256KB L2 (shared w/ 2 CPUs), 4MB L3 and Cortex-A510 (2022) using 32KB L1, 256KB L2(shared w/ 2 CPUs), 4MB L3 (iso-process, iso-frequency).

⁵ aarch64 vs aarach32 LITTLE core performance. Relative SPECint 2k6 scores.

Re-use is only permitted for informational and non-commerical or personal use only.