#### Hardware Support for ACID Transactions in Persistent Memory Systems

#### **ARM Research Summit, 2018**

#### <u>Arpit Joshi</u>

#### CSOInstitute for ComputingSystems Architecture

#### Vijay Nagarajan

- Marcelo Cintra

- Stratis Viglas

#### Collaborators

### Persistent Memory is here...

### Persistent Memory is here...

#### Intel Displays 512GB Optane DC Persistent Memory DIMMs

by Paul Alcorn May 31, 2018 at 2:02 AM

Intel held its Memory and Storage day today at its Santa Clara headquarters to announce its Optane DC Persistent Memory DIMMs. The new DIMMs slot into the DRAM interface, just like a normal stick of RAM, but come in three capacities of 128, 256, and 512GB. That's a massive capacity increase compared to the industry-leading 128GB DDR4 memory sticks. Intel designed the DIMMs to bridge both the performance and pricing gap between storage and memory, so the new DIMMs should land at much lower price points than typical DRAM.

**NOW SHIPPING SAMPLES**

**BROAD DEVELOPER ENGAGEMENT**

**Big and Affordable Memory**

**High Performance Storage**

Direct Load/Store Access

128, 256, 512GB

DDR4 Pin Compatible

Hardware Encryption

**High Reliability**

#### Intel teases Optane DIMMS, but you may need a new Xeon first

128GB, 256GB and 512GB modules offered as new storage tier below RAM, above SSD

By Simon Sharwood, APAC Editor 31 May 2018 at 03:50

5 🖵 SHARE V

#### Intel Launches Optane DIMMs Up To 512GB:

Intel's new Optane DC persistent memory DIMM. (C

- Persistent Memory

- Non-volatility over the memory bus

- Load/Store interface to persistent data

- Persistent Memory

- Non-volatility over the memory bus

- Load/Store interface to persistent data

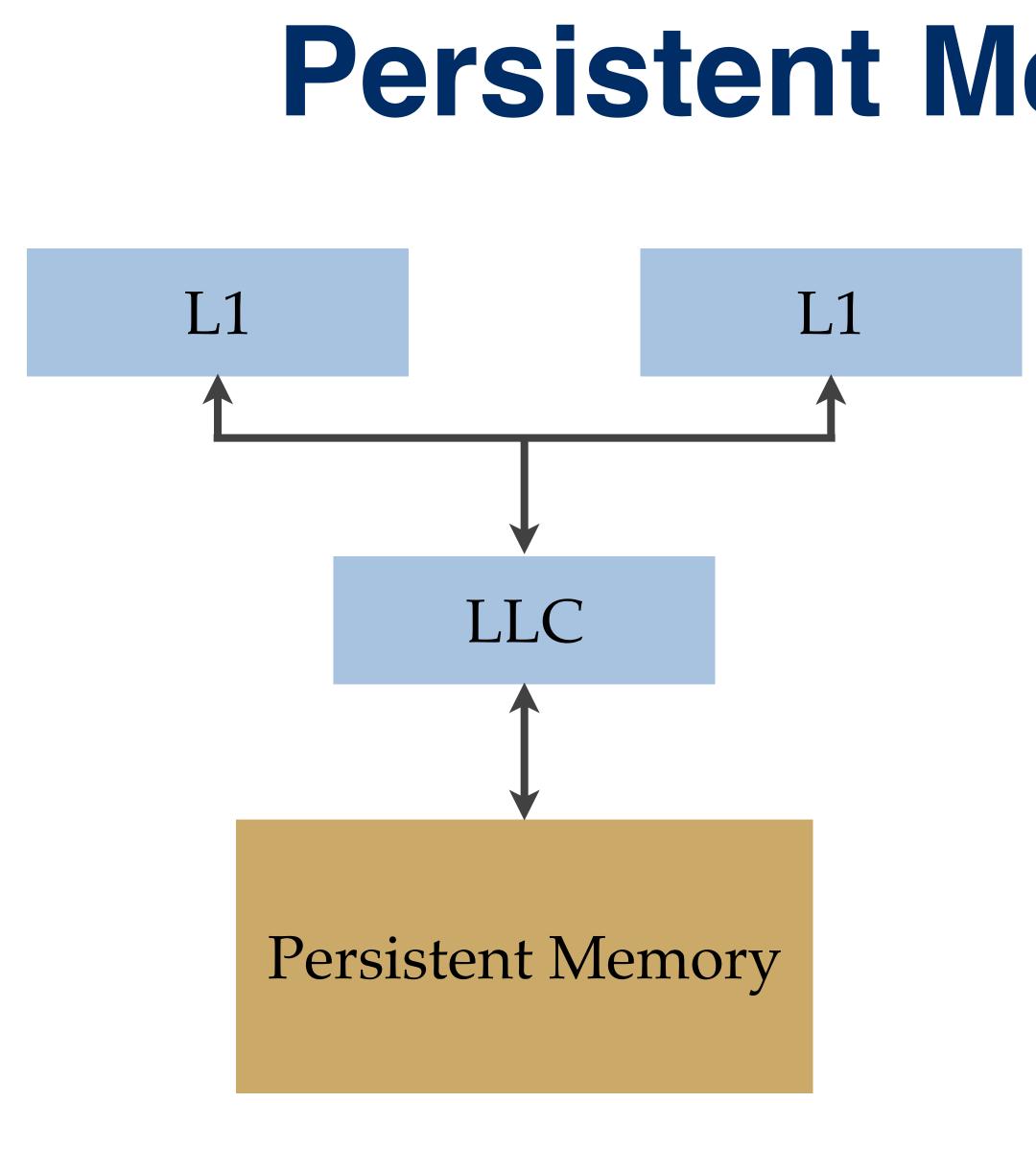

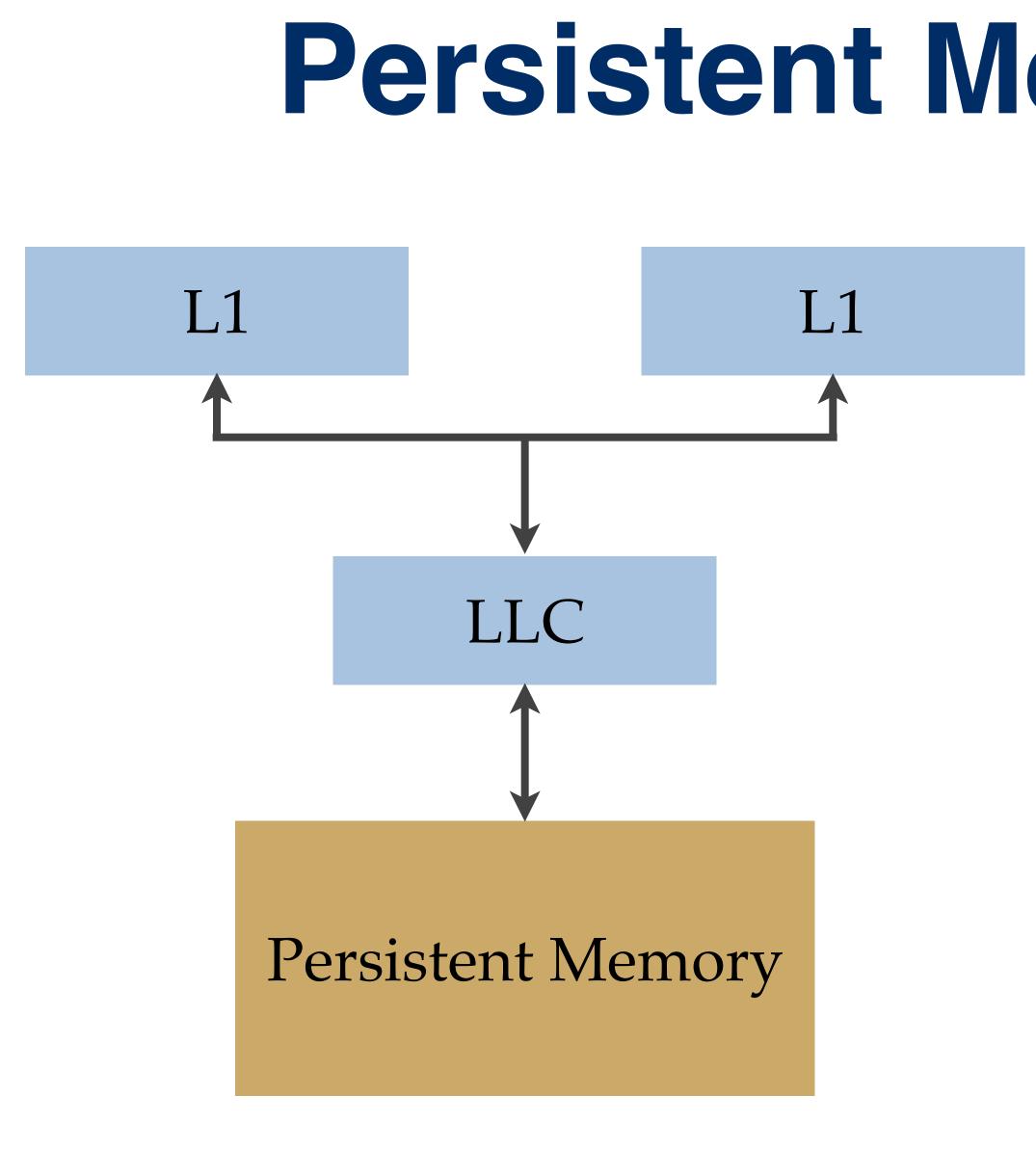

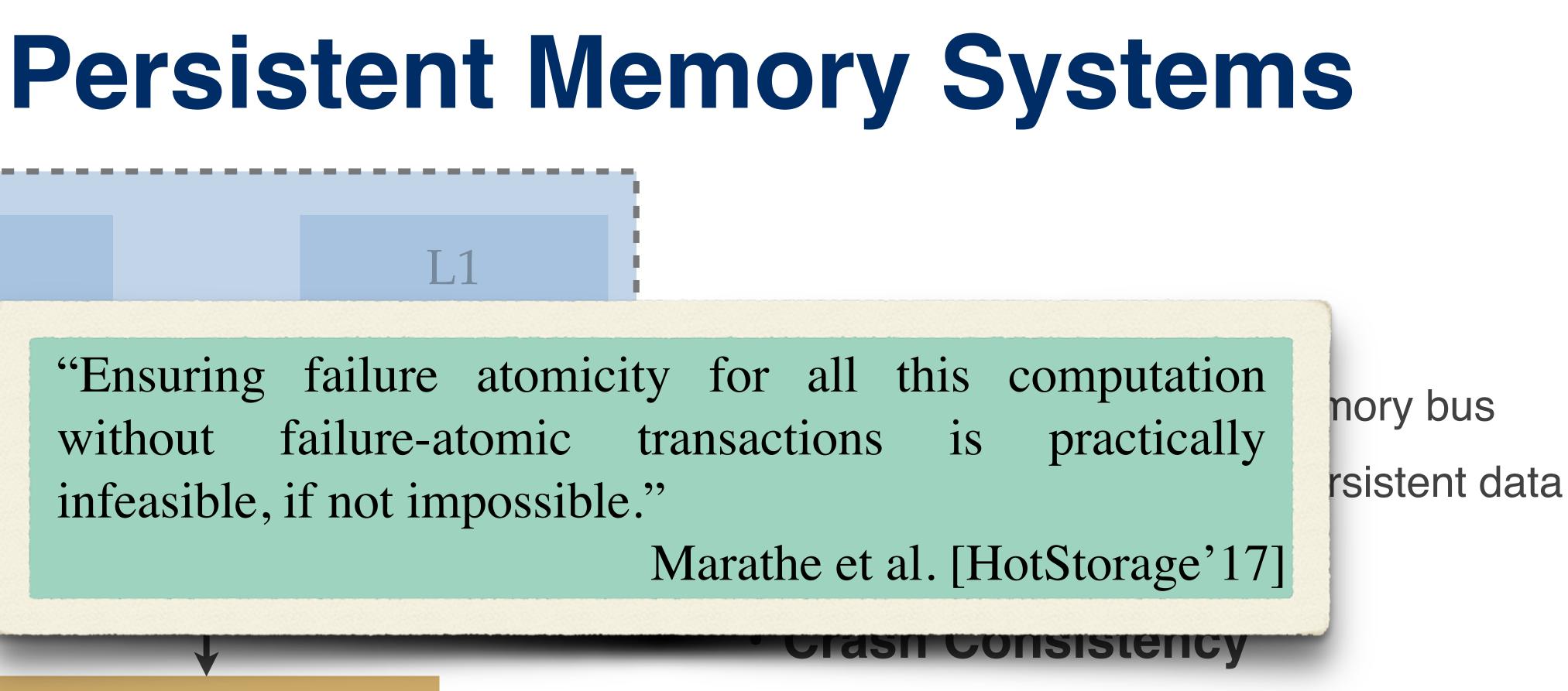

#### Persistent Memory

- Non-volatility over the memory bus

- Load/Store interface to persistent data

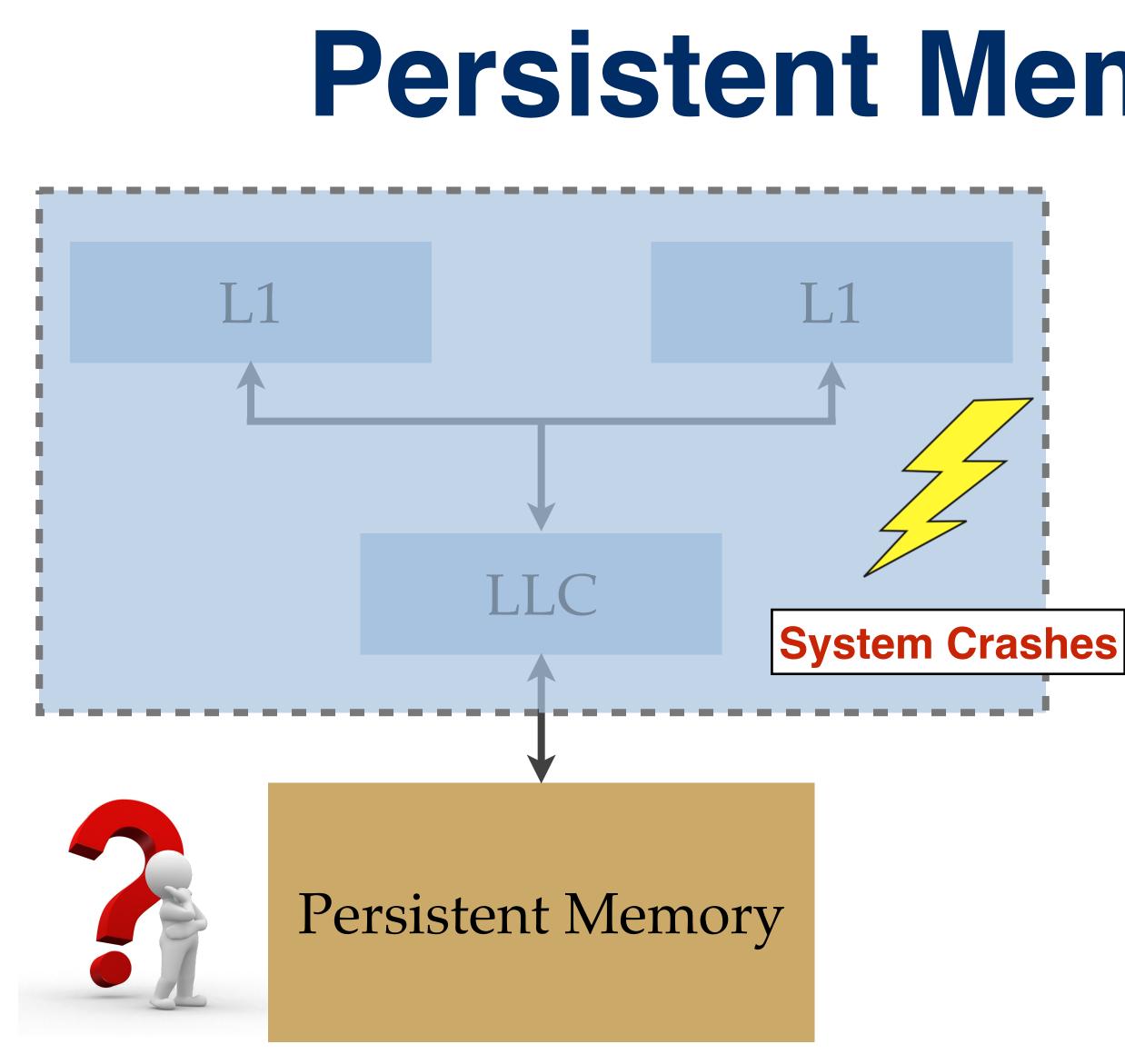

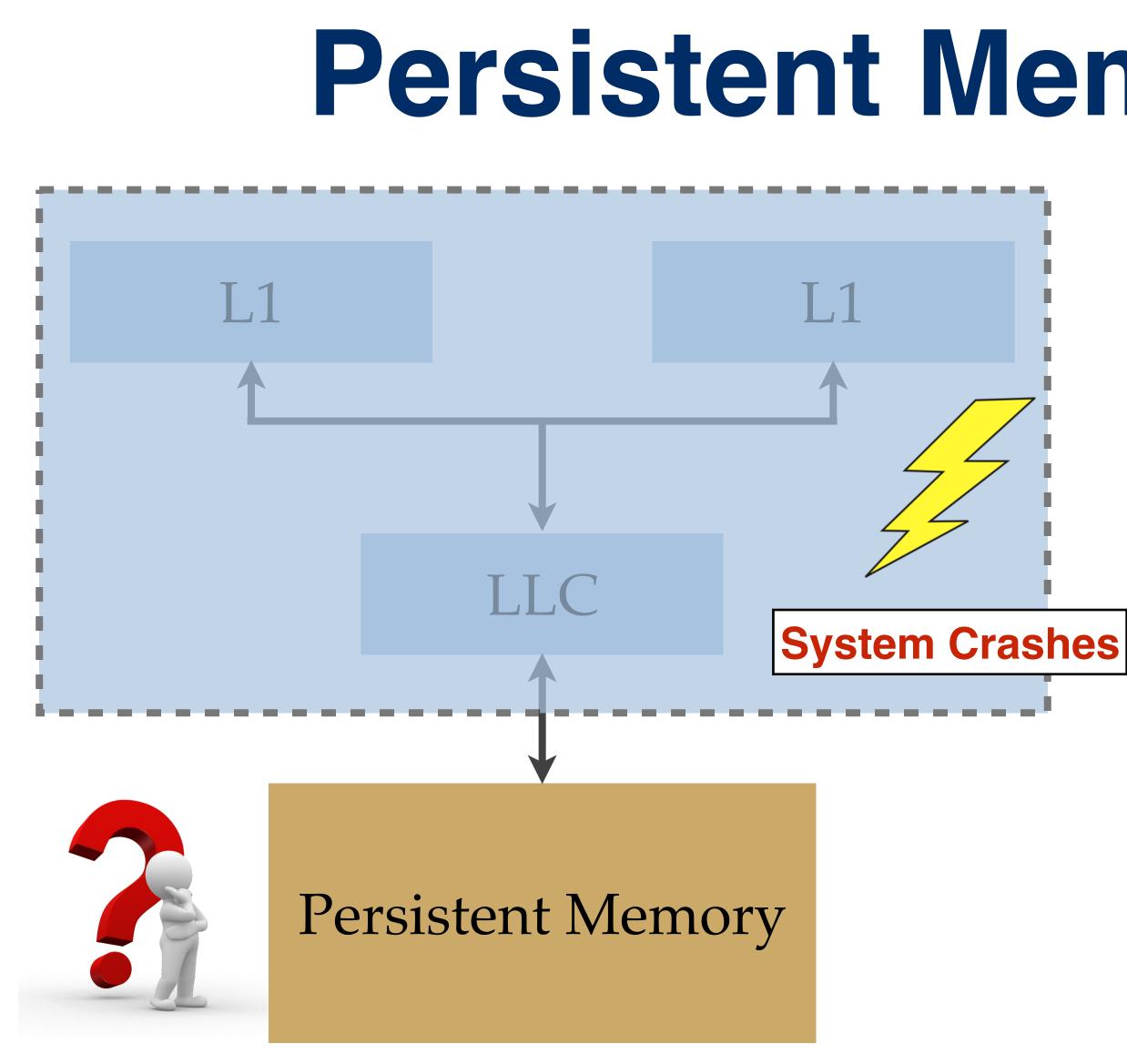

#### Crash Consistency

- Is the persistent state consistent?

- Programming Model: ACID Transactions -

# infeasible, if not impossible."

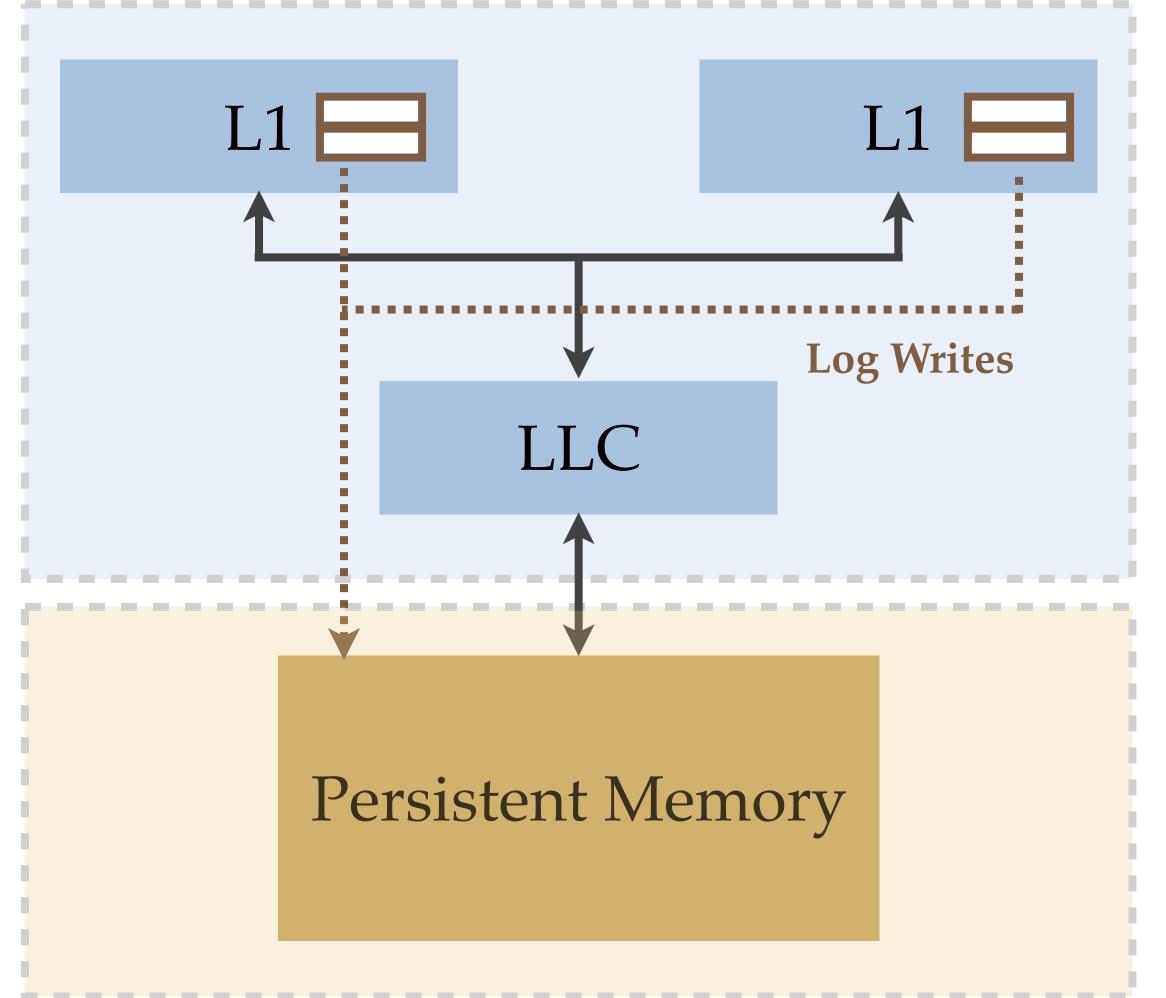

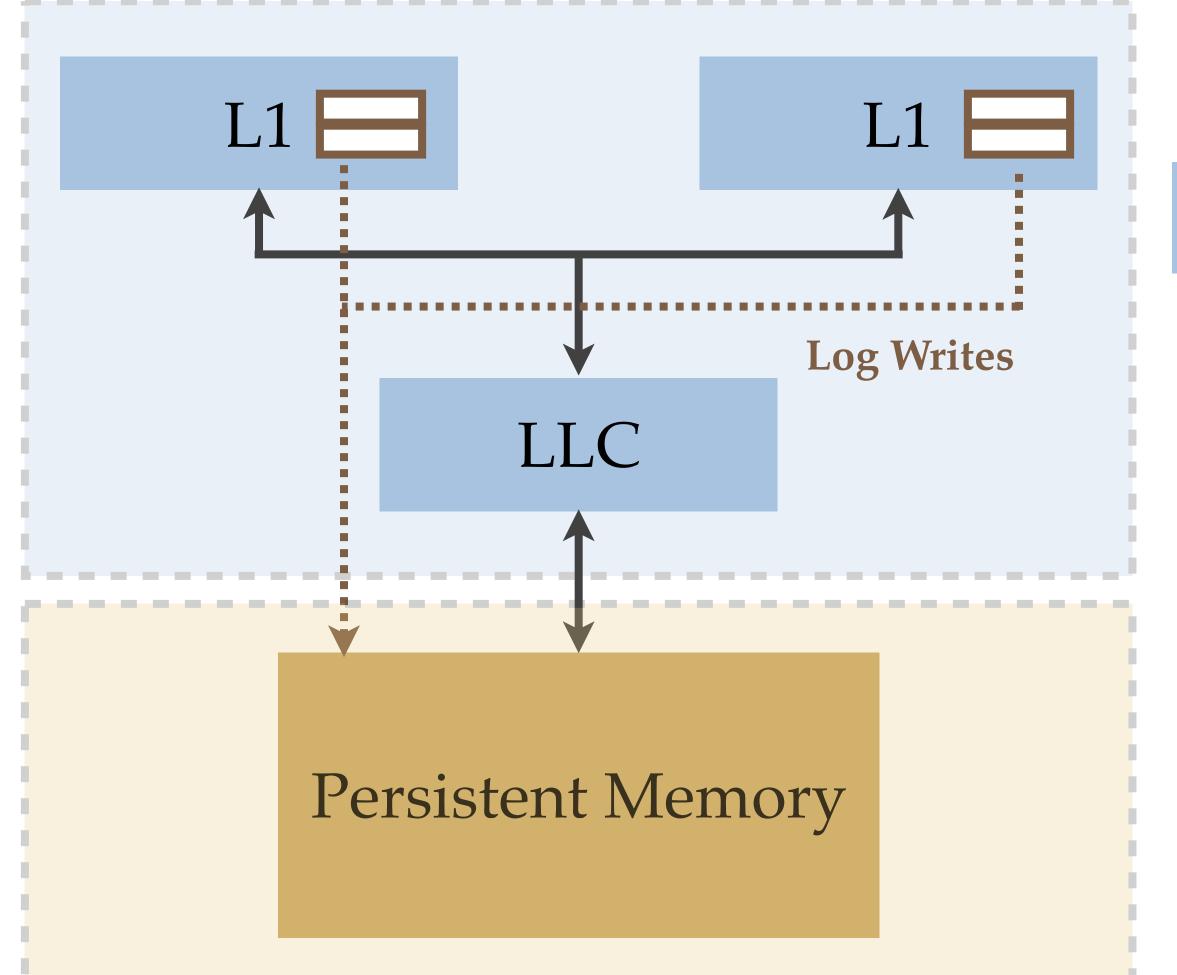

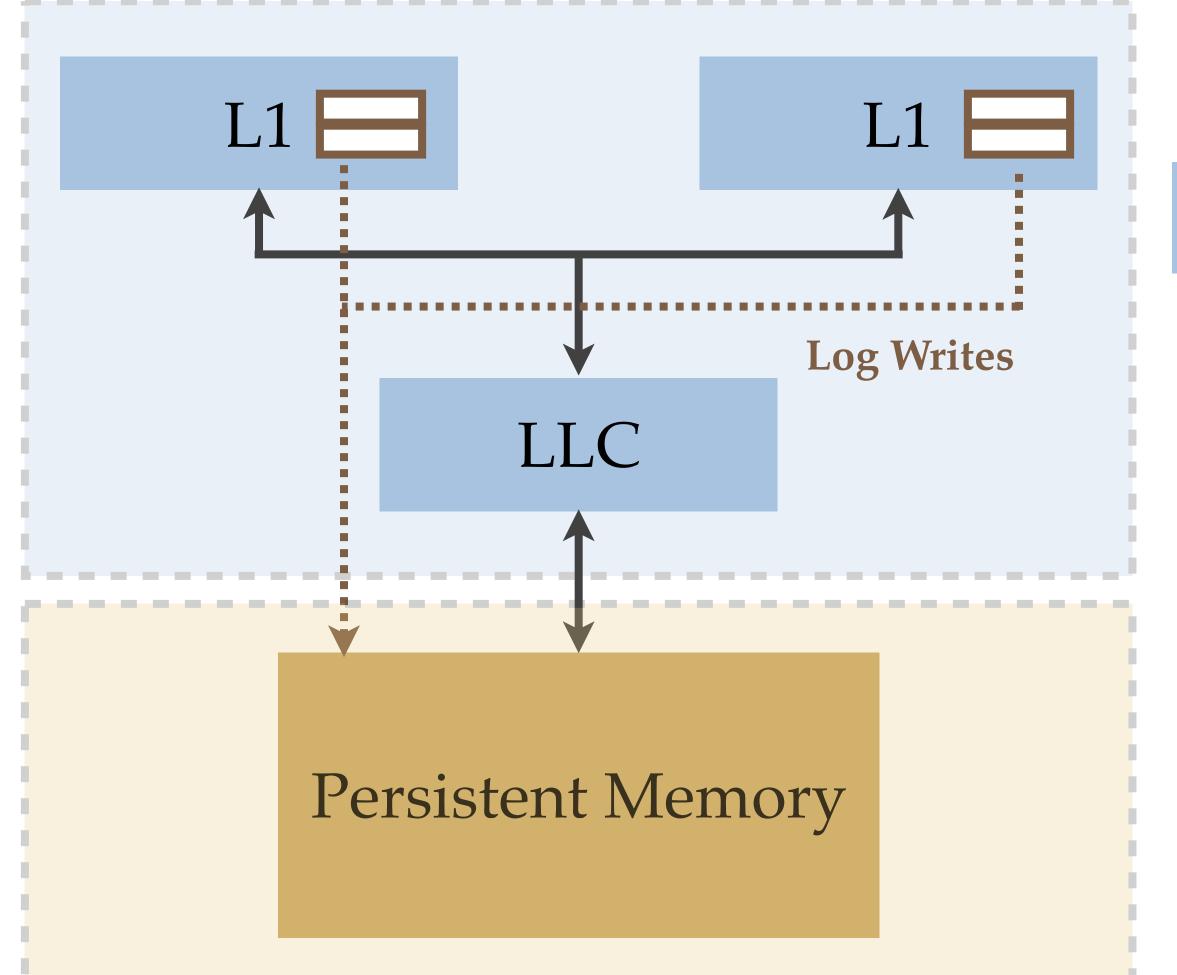

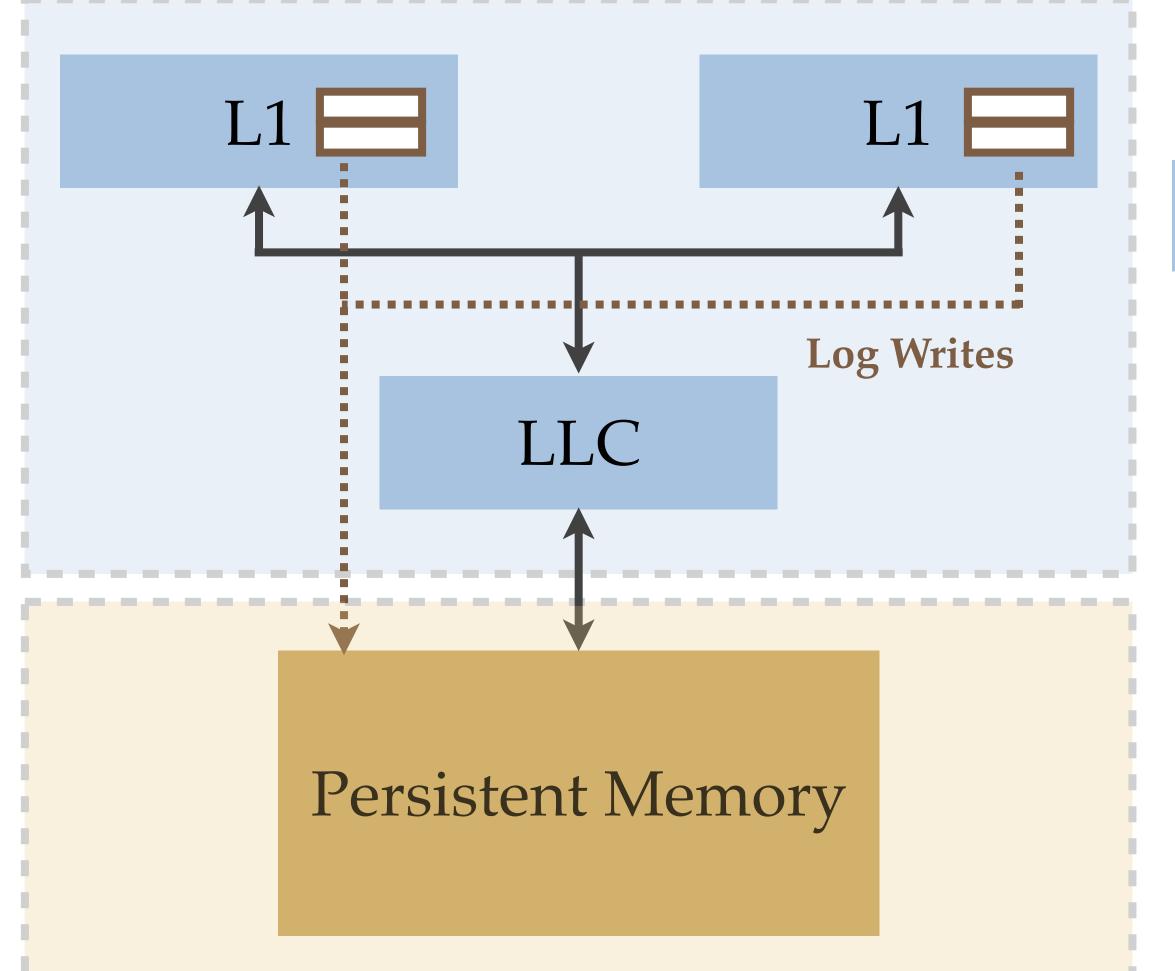

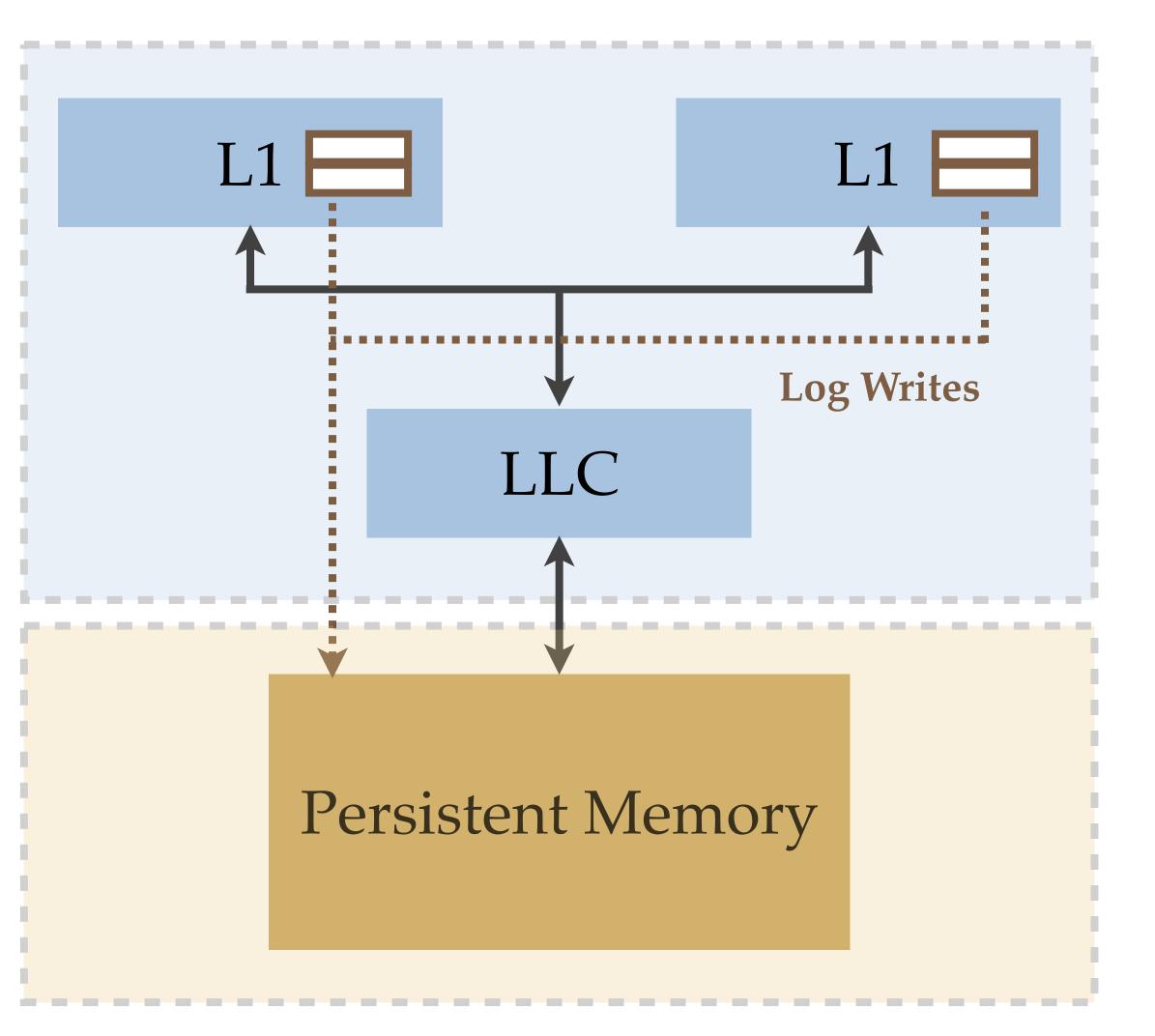

L1

L1

Persistent Memory

- Is the persistent state consistent?

- Programming Model: ACID Transactions -

# infeasible, if not impossible."

L1

L1

Persistent Memory

#### How fast can we support ACID?

- Is the persistent state consistent?

- Programming Model: ACID Transactions -

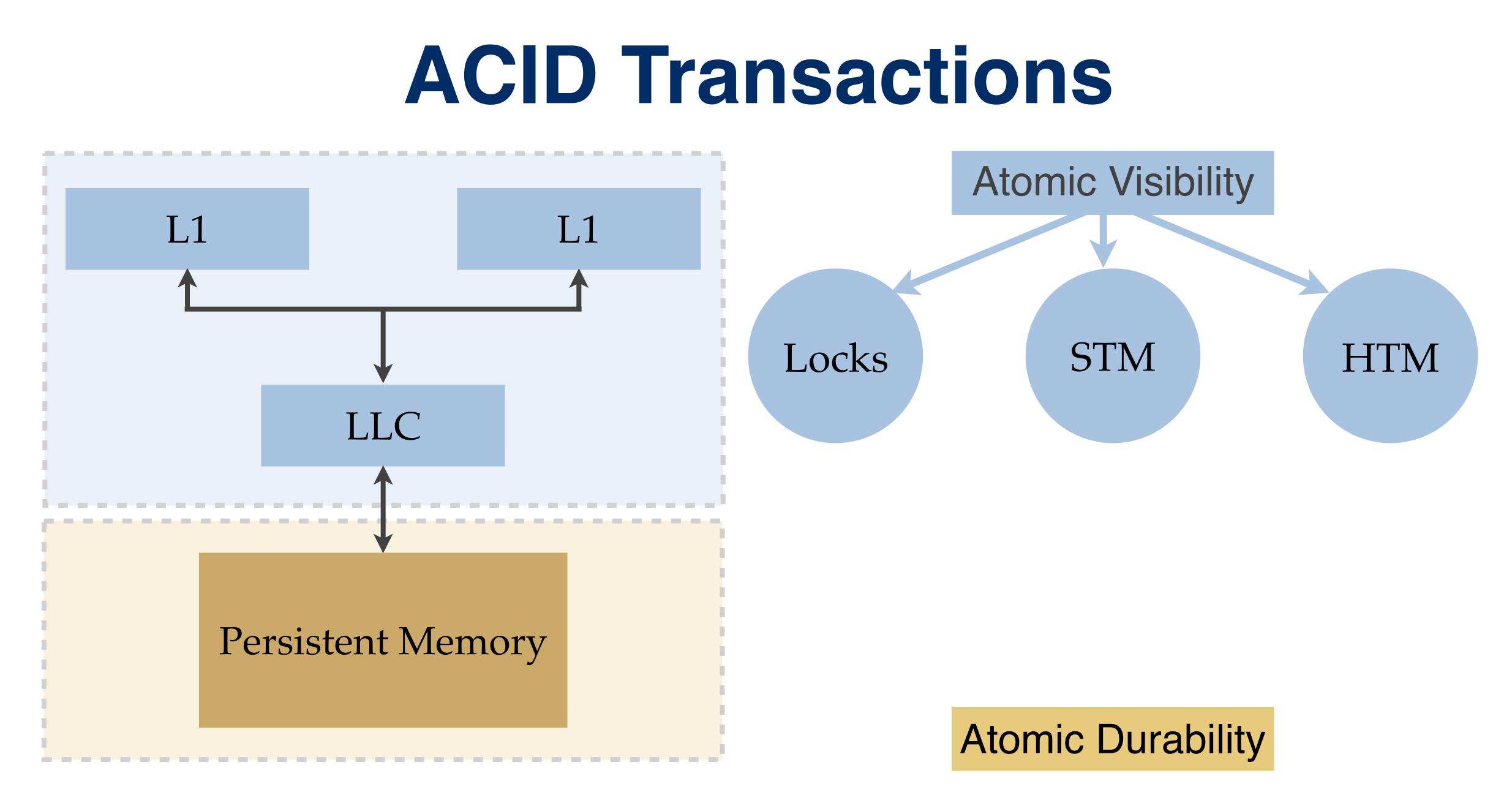

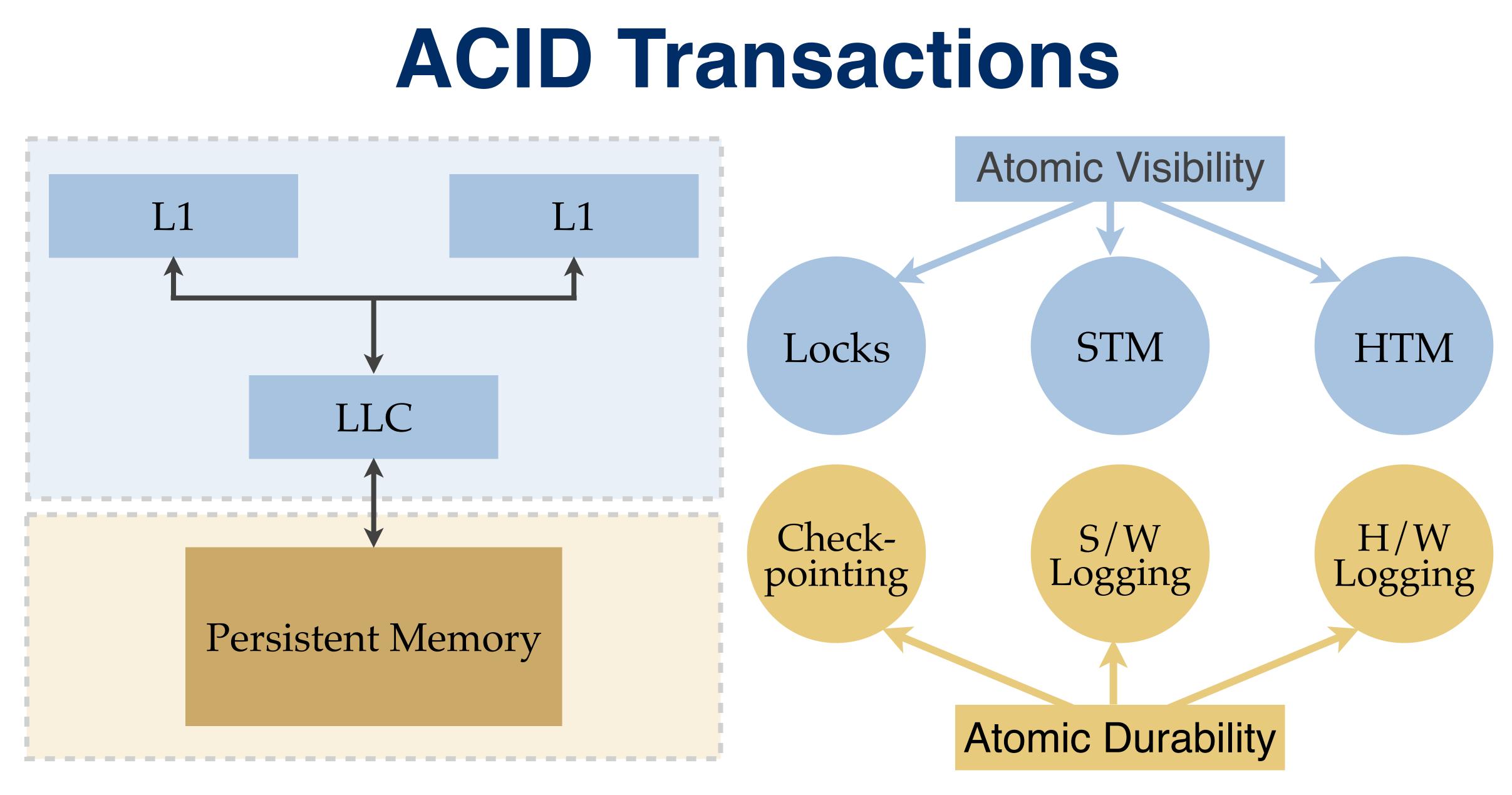

#### **ACID Transactions**

#### **ACID Transactions**

#### Atomic Visibility

#### **ACID Transactions**

#### Atomic Visibility

**Atomic Durability**

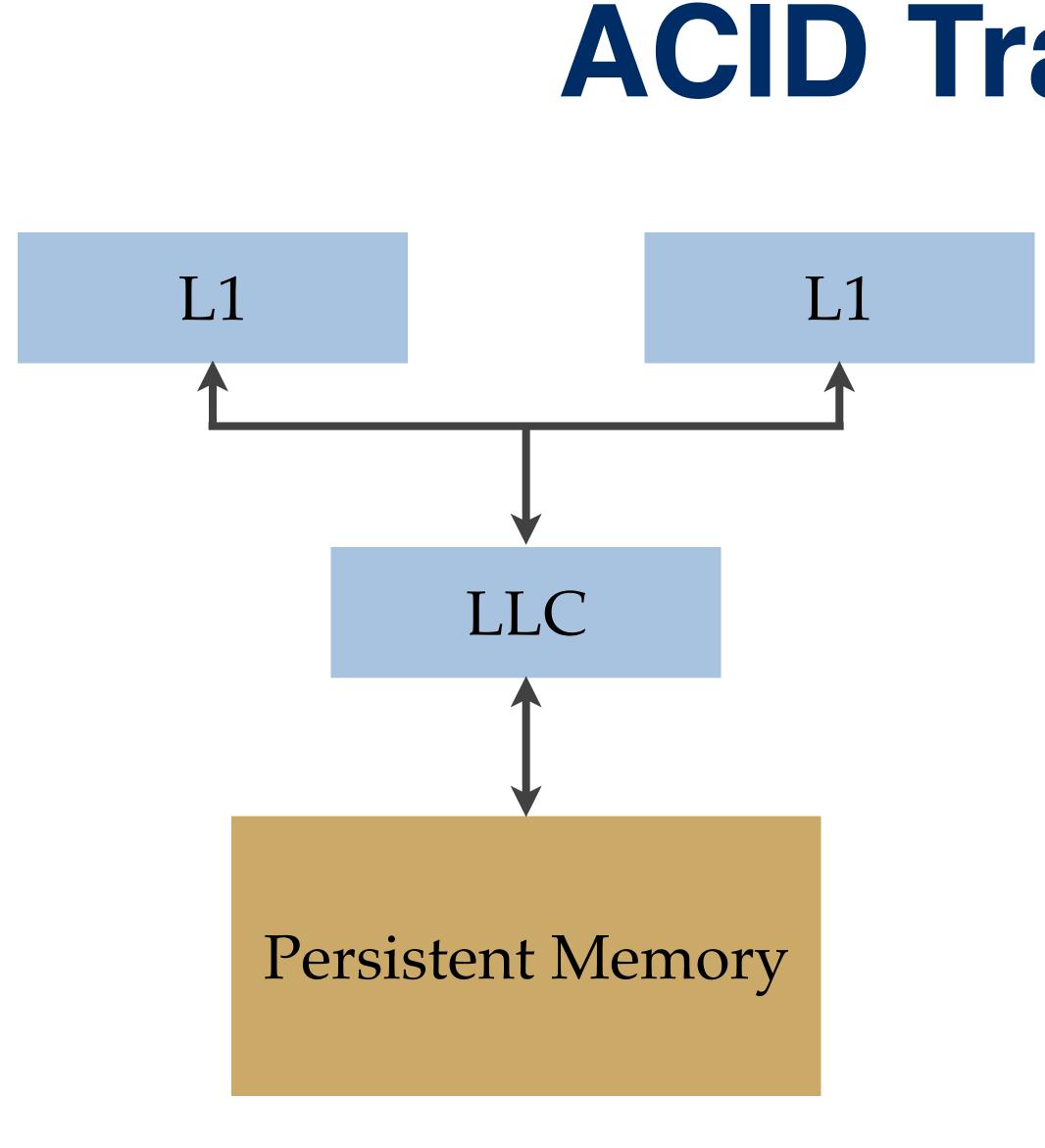

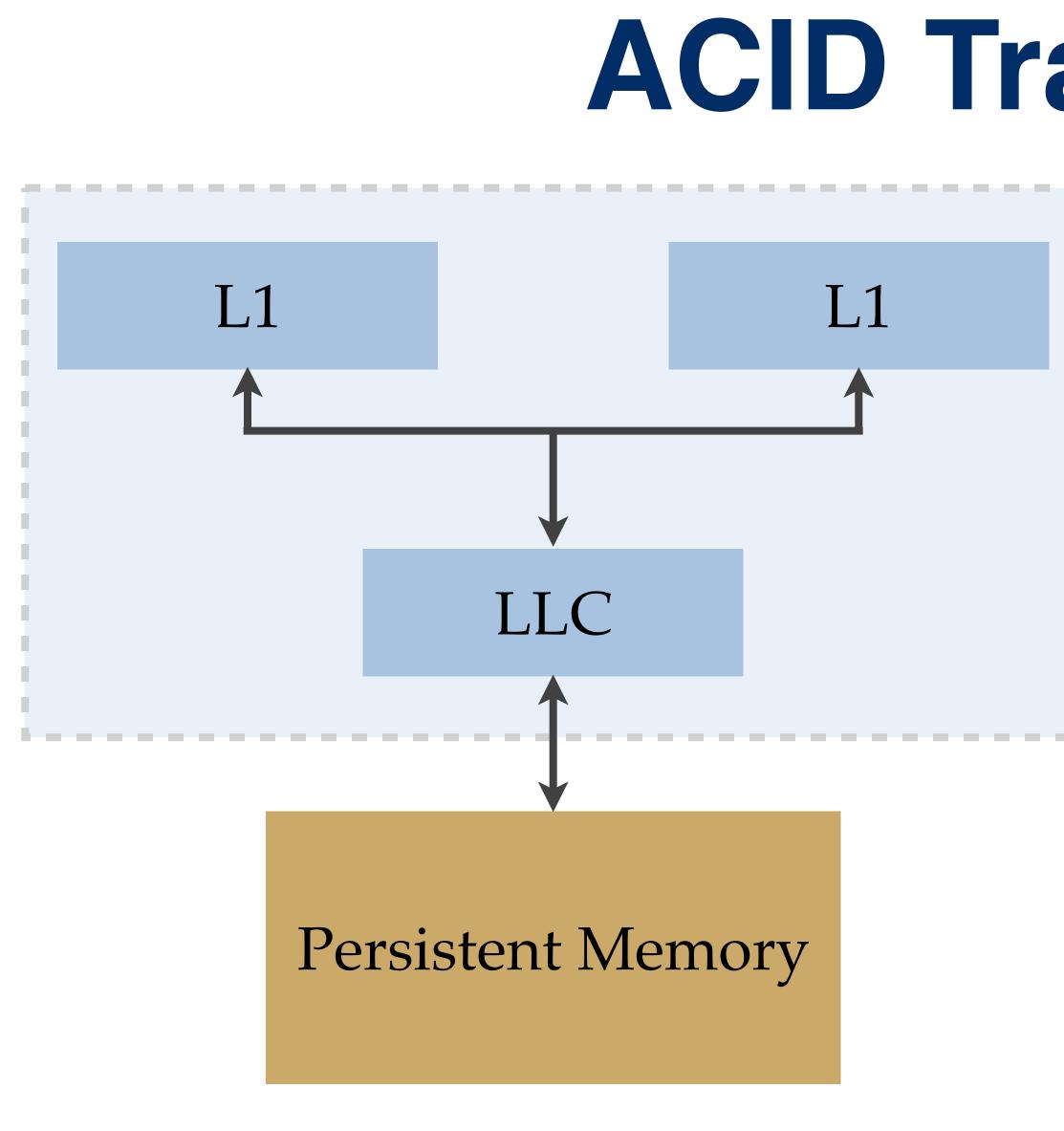

#### Commercial HTMs [Intel, IBM]

#### Commercial HTMs [Intel, IBM]

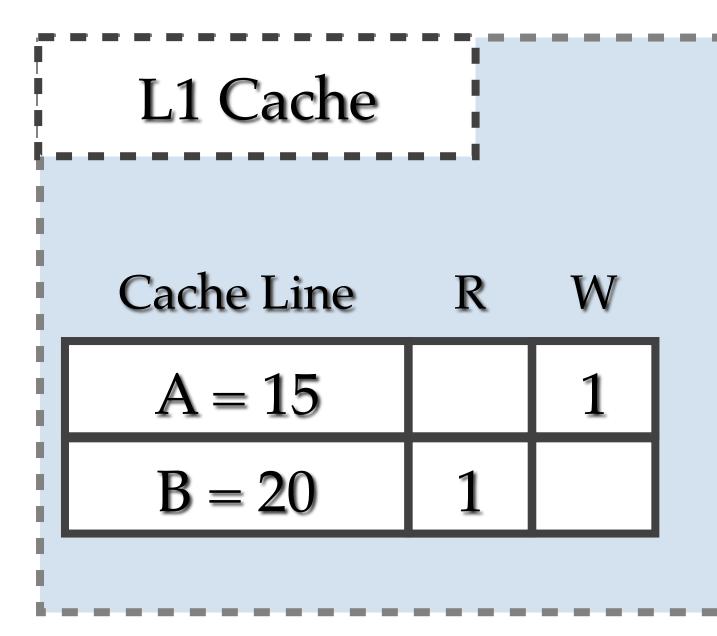

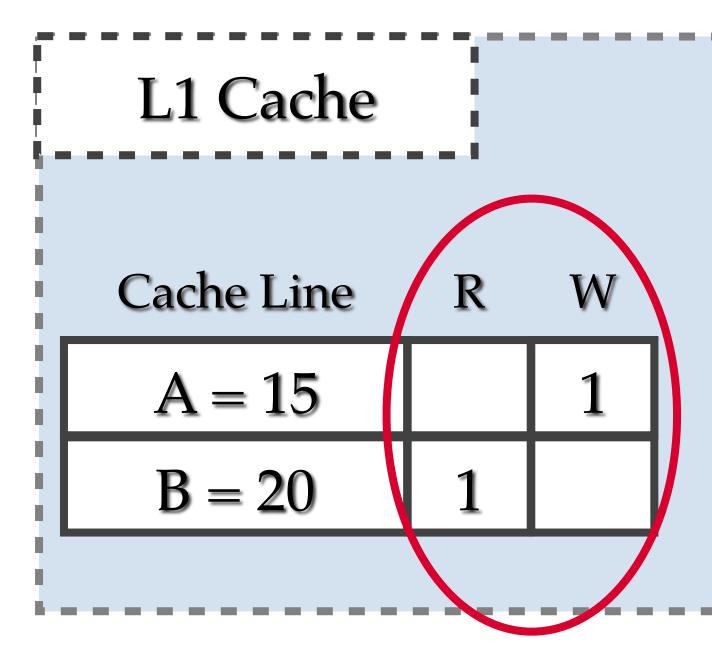

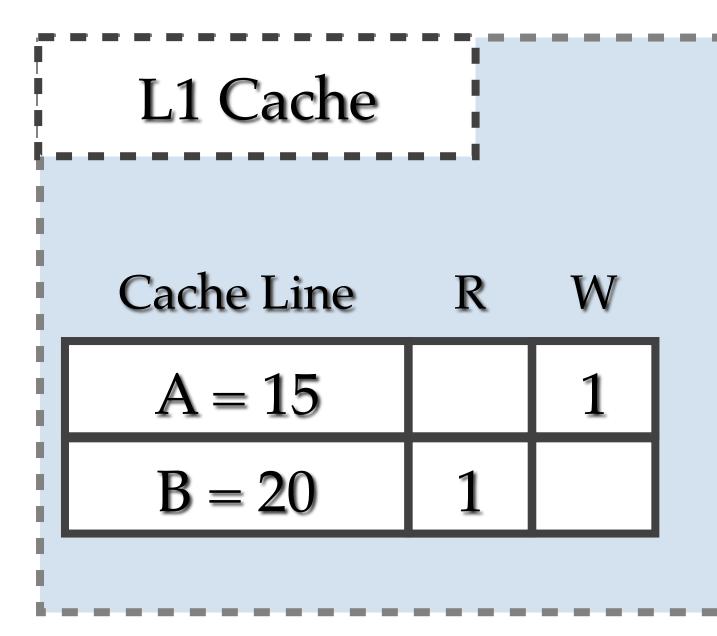

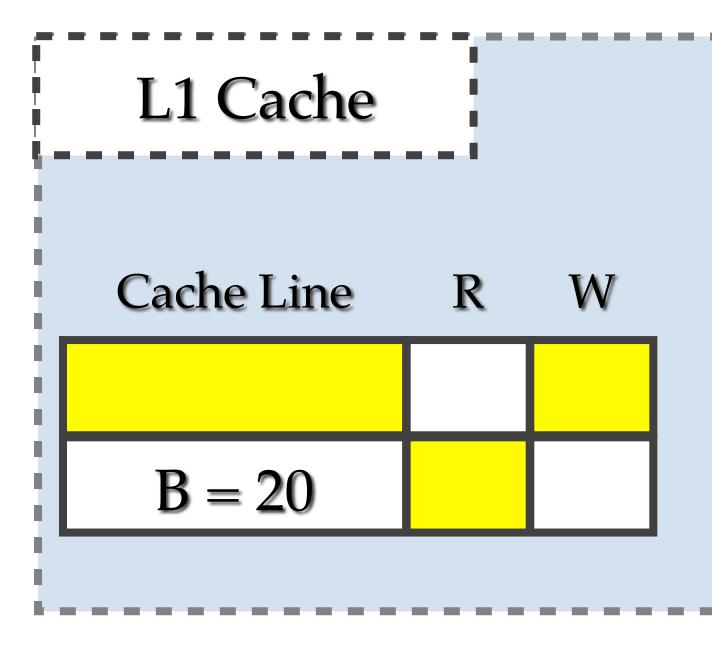

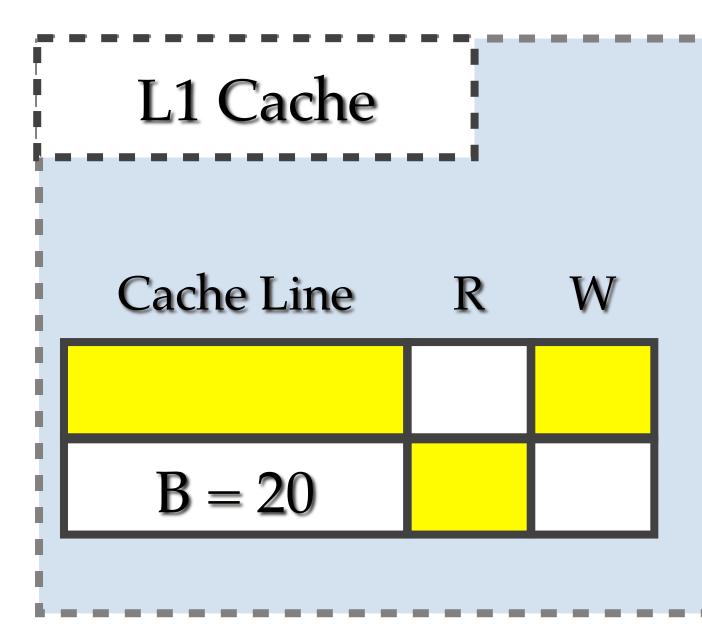

- Version Management: read/write sets in L1 cache

- Commercial HTMs [Intel, IBM]

- Version Management: read/write sets in L1 cache

- **Conflict Detection**: piggy back on the coherence protocol

- Commercial HTMs [Intel, IBM]

- Version Management: read/write sets in L1 cache

- **Conflict Detection**: piggy back on the coherence protocol

- **Commit:** make updates non-speculative

#### • Commercial HTMs [Intel, IBM]

- Version Management: read/write sets in L1 cache

- **Conflict Detection**: piggy back on the coherence protocol

- **Commit:** make updates non-speculative

- **Abort**: invalidate write set

- Commercial HTMs [Intel, IBM]

- Version Management: read/write sets in L1 cache

- **Conflict Detection**: piggy back on the coherence protocol

- **Commit:** make updates non-speculative

- **Abort**: invalidate write set

Write-sets in commercial HTMs limited by the size of the L1 cache.

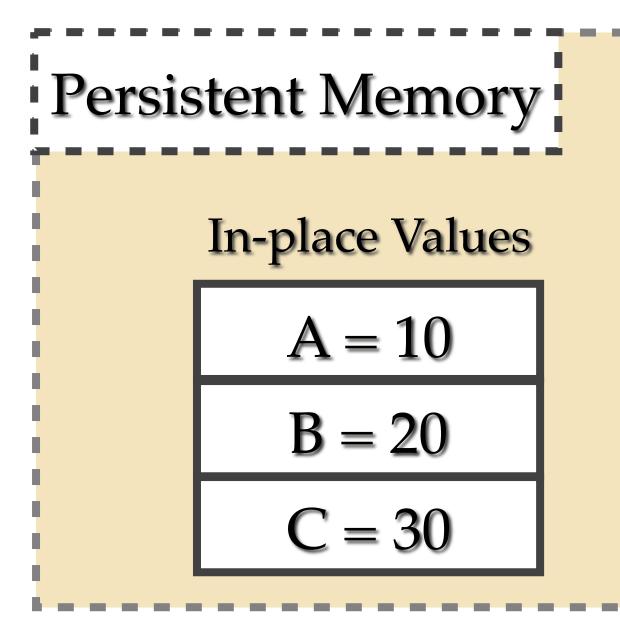

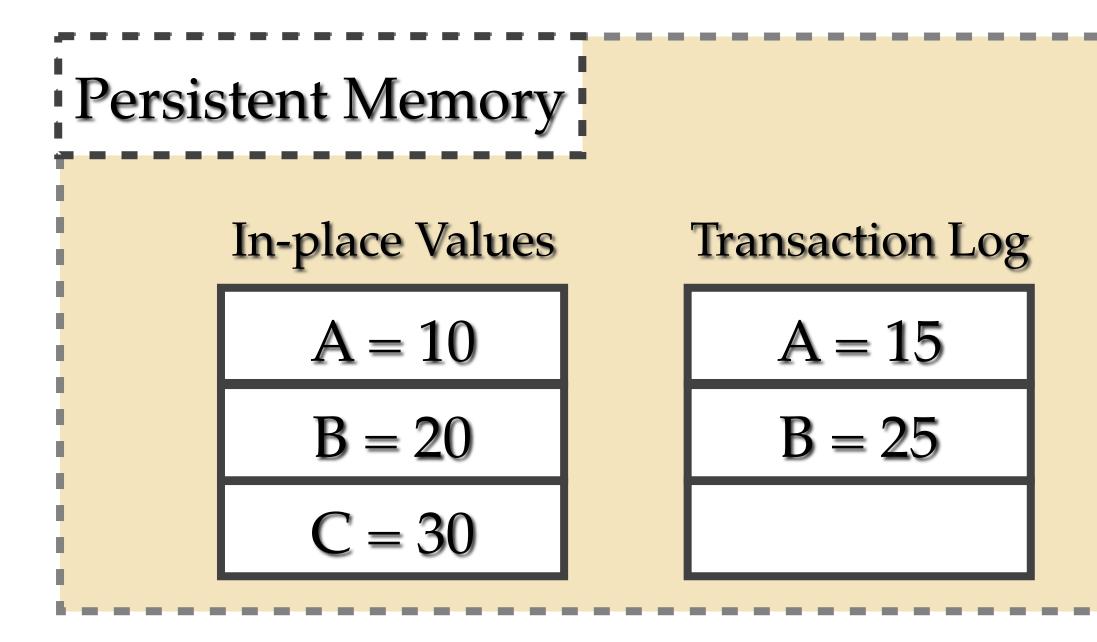

### • Logging for durability [Doshi'16, Joshi'17, Shin'17, Ogleari'18]

#### Logging for durability [Doshi'16, Joshi'17, Shin'17, Ogleari'18]

- Write a log entry for every update

- Logging for durability [Doshi'16, Joshi'17, Shin'17, Ogleari'18]

- Write a log entry for every update

- Commit: Update the values in-place

- Logging for durability [Doshi'16, Joshi'17, Shin'17, Ogleari'18]

- Write a log entry for every update

- Commit: Update the values in-place

- Abort: Undo any in-place updates

In-place updates in the critical path of commit

High memory write bandwidth requirement

- Logging for durability [Doshi'16, Joshi'17, Shin'17, Ogleari'18]

- Write a log entry for every update

- Commit: Update the values in-place

- Abort: Undo any in-place updates

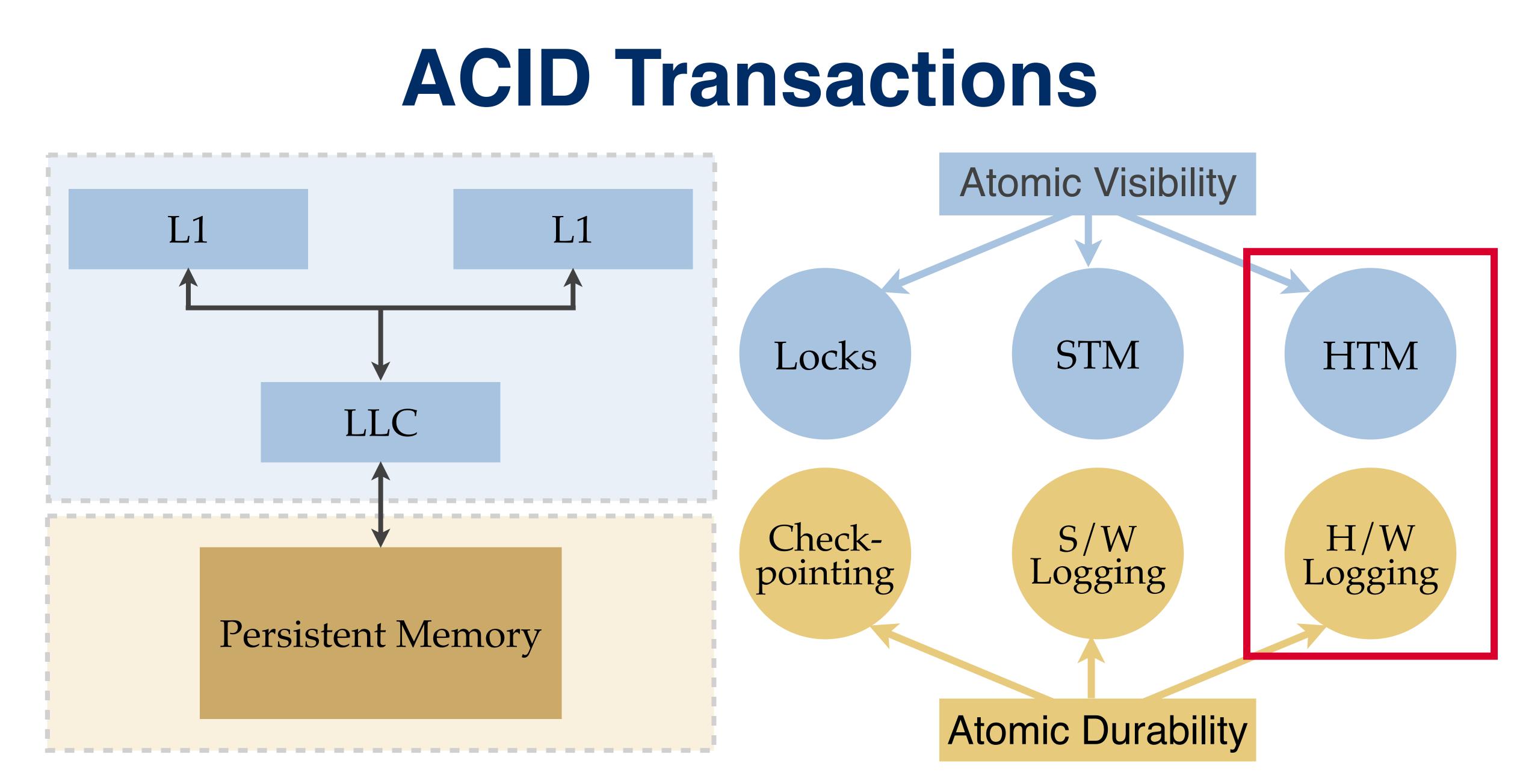

## ACID = HTM + Logging

#### **Goals:**

- Support fast commits

- Minimise memory bandwidth consumption

- Extend the supported transaction size

- Maintain the simplicity of commercial HTMs

#### width consumption ansaction size of commercial HTMs

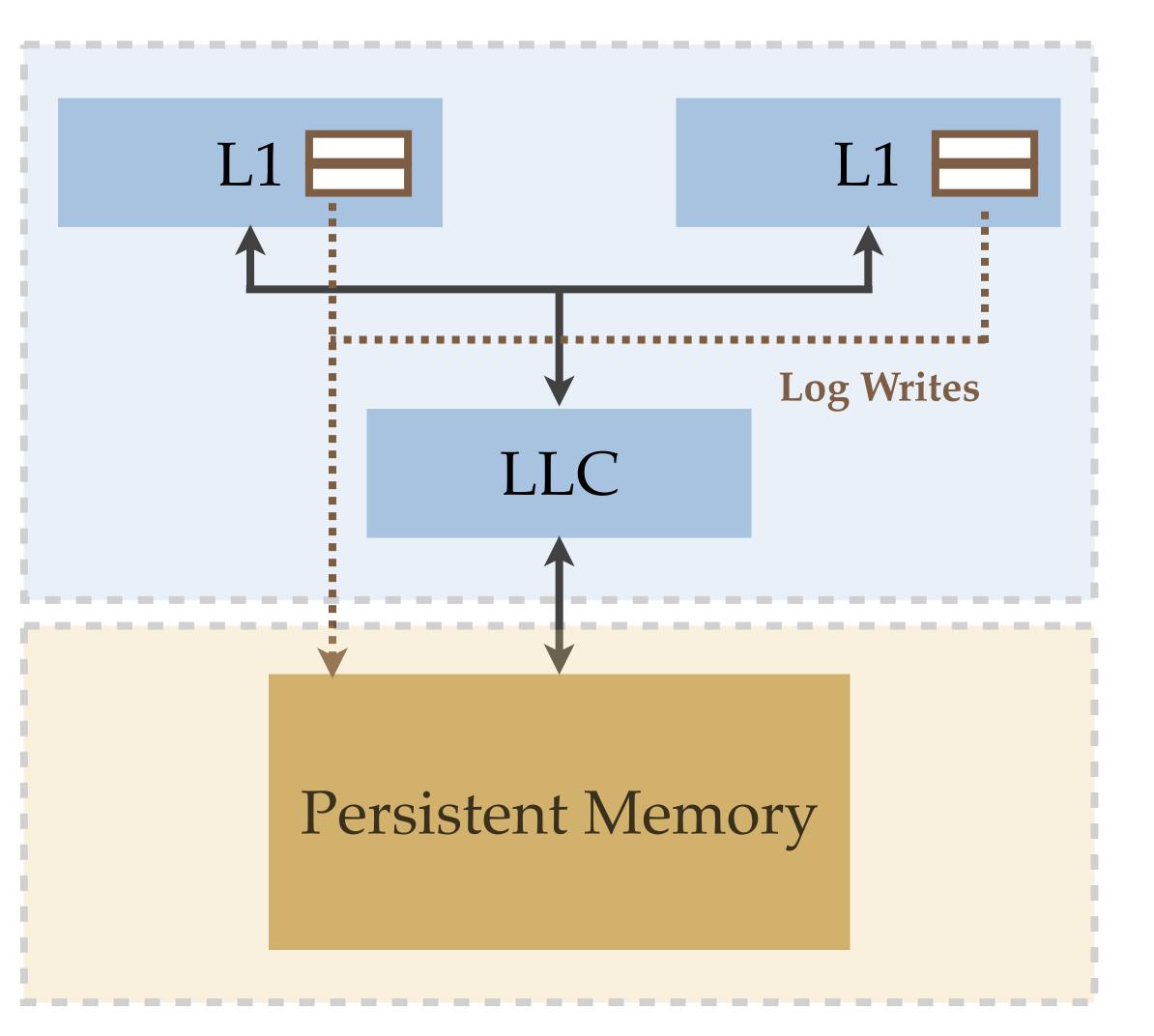

#### **Commercial HTM + Hardware Redo Log**

#### **Commercial HTM + Hardware Redo Log**

- H/W Redo Log + Log Buffer

- Reduced memory bandwidth

- Fast commits

#### **Commercial HTM + Hardware Redo Log**

- H/W Redo Log + Log Buffer

- Reduced memory bandwidth

- Fast commits

- H/W Log + Sticky State

- Extended transaction size to the LLC

- Simplicity of commercial HTM

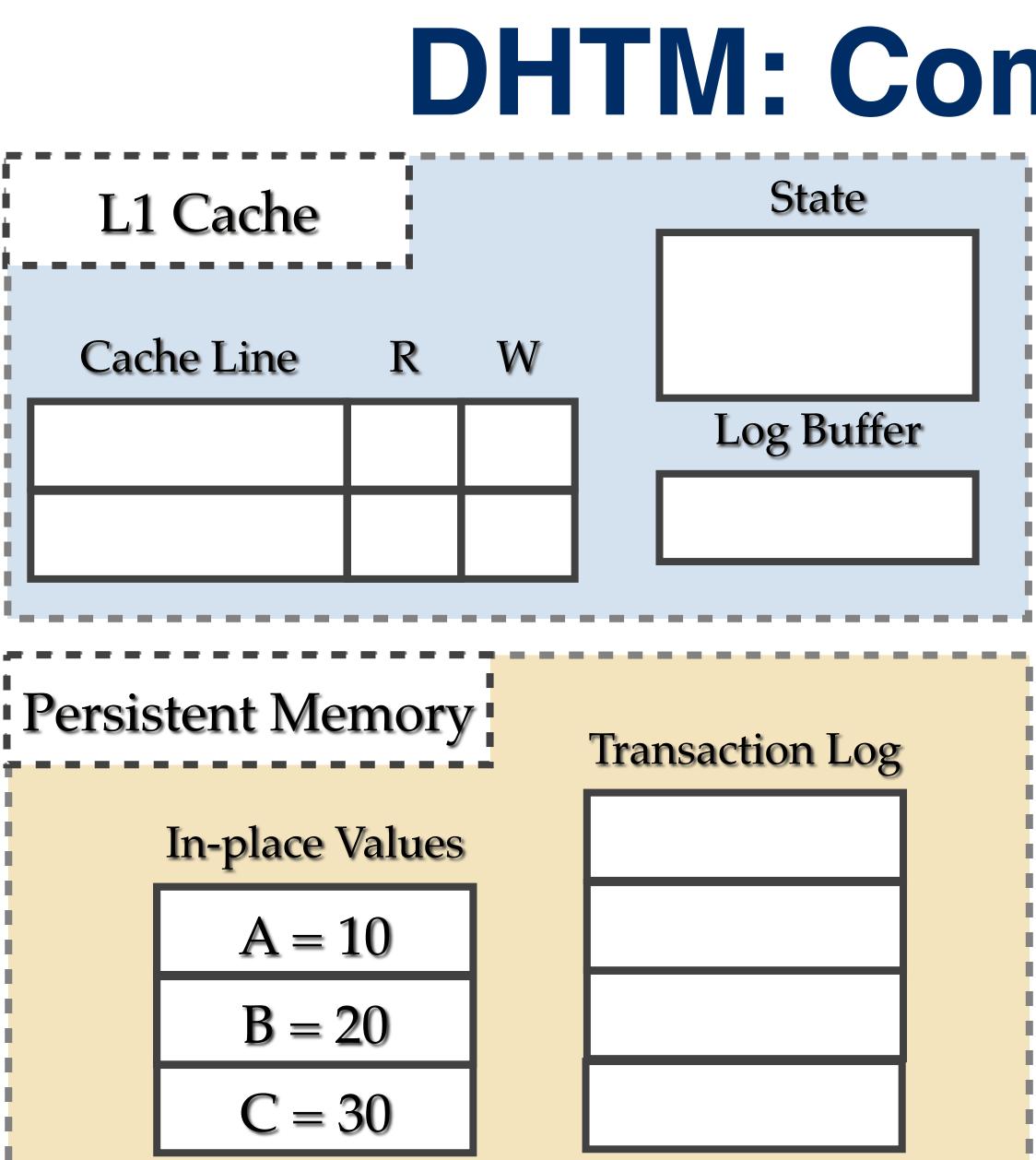

### DHTM: Log Buffer

### DHTM: Log Buffer

Redo Log Bandwidth Problem

## Redo Log Bandwidth Problem

## - write a log entry for every store

- Redo Log Bandwidth Problem

- write a log entry for every store

- multiple stores create multiple log entries

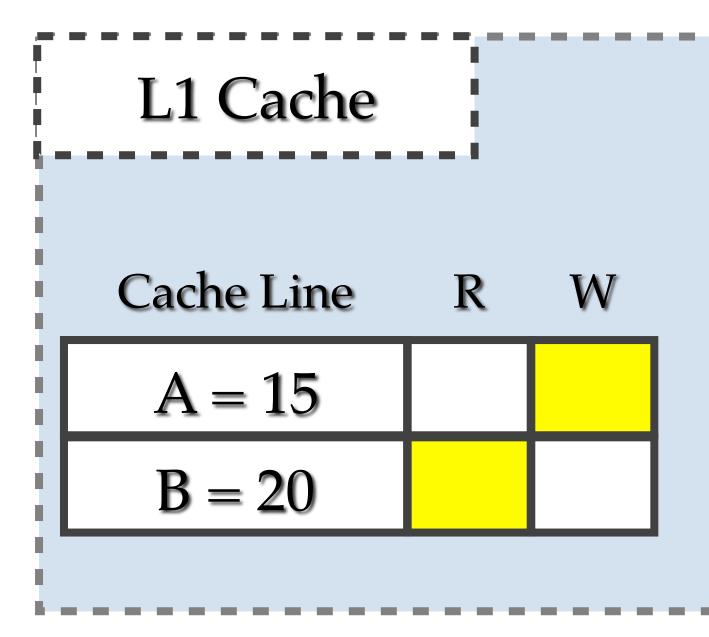

- **Redo Log Bandwidth Problem**

- write a log entry for every store

- multiple stores create multiple log entries

- Solution: Log Buffer

- **Redo Log Bandwidth Problem**

- write a log entry for every store

- multiple stores create multiple log entries

## Solution: Log Buffer

- track cache lines being modified

- **Redo Log Bandwidth Problem**

- write a log entry for every store

- multiple stores create multiple log entries

## Solution: Log Buffer

- track cache lines being modified

- multiple writes coalesced in a log entry

- **Redo Log Bandwidth Problem**

- write a log entry for every store

- multiple stores create multiple log entries

## Solution: Log Buffer

- track cache lines being modified

- multiple writes coalesced in a log entry -

- log entry written to persistent memory on eviction from log buffer

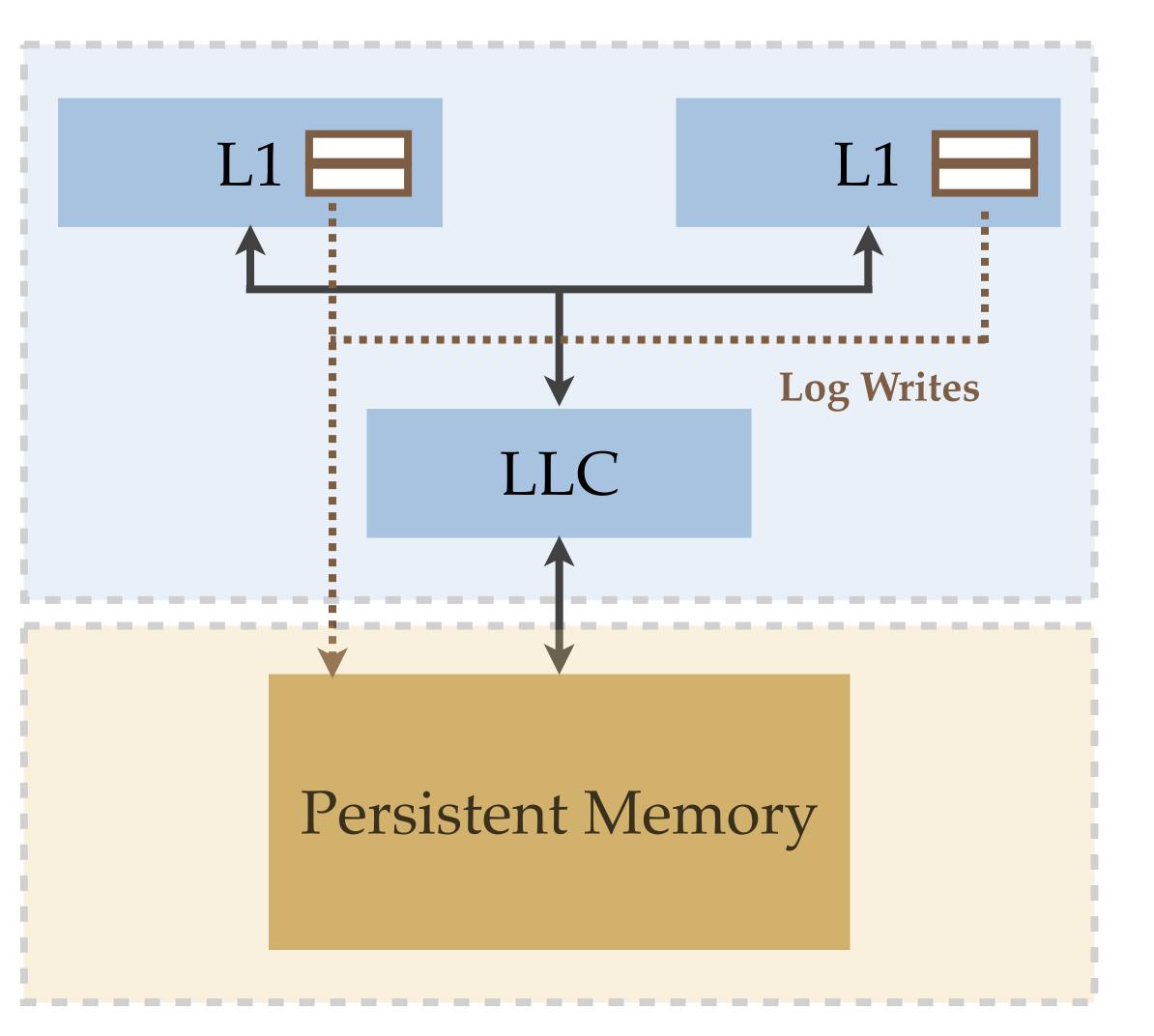

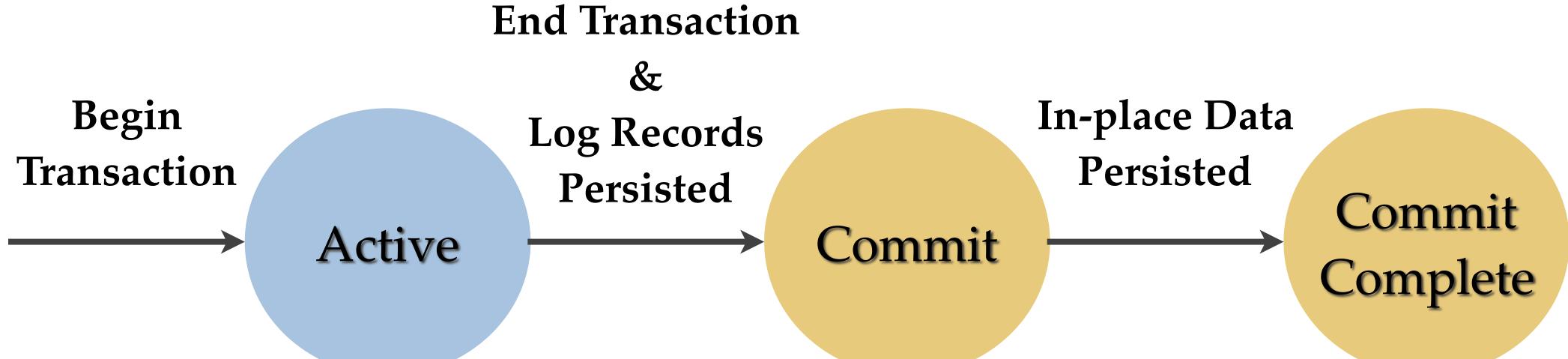

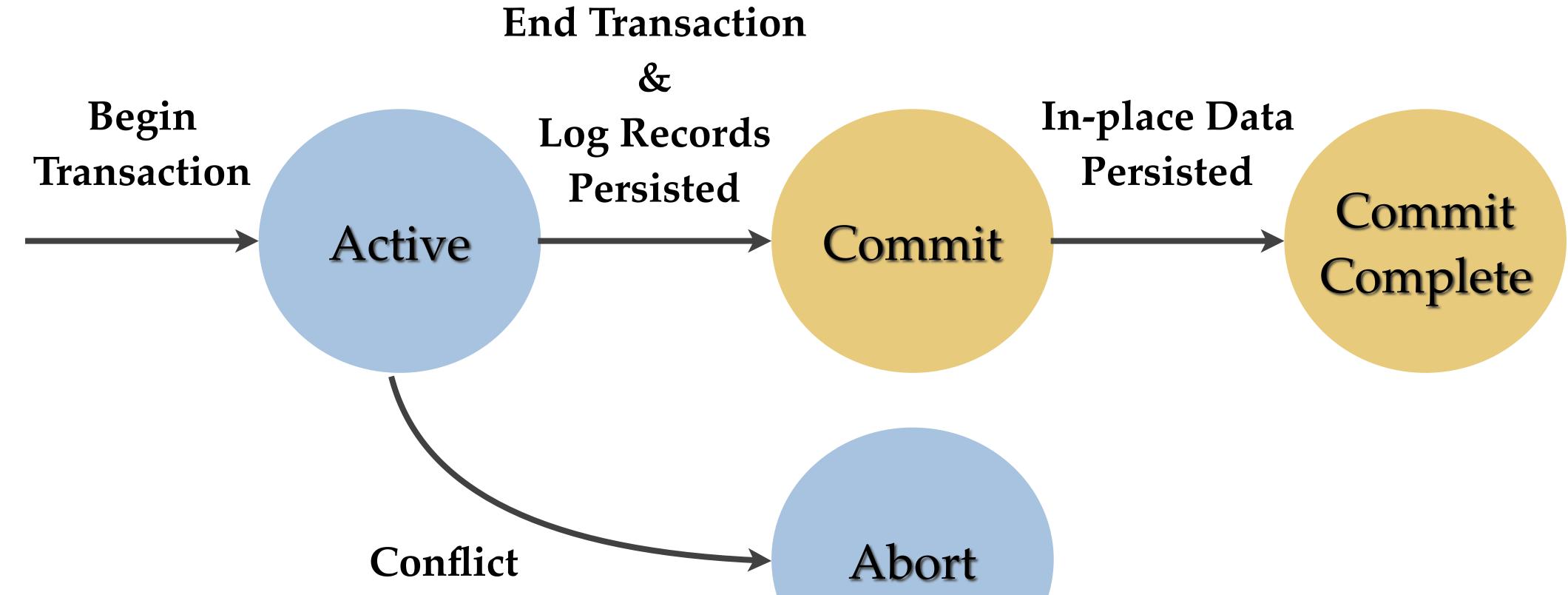

## Begin Transaction Active

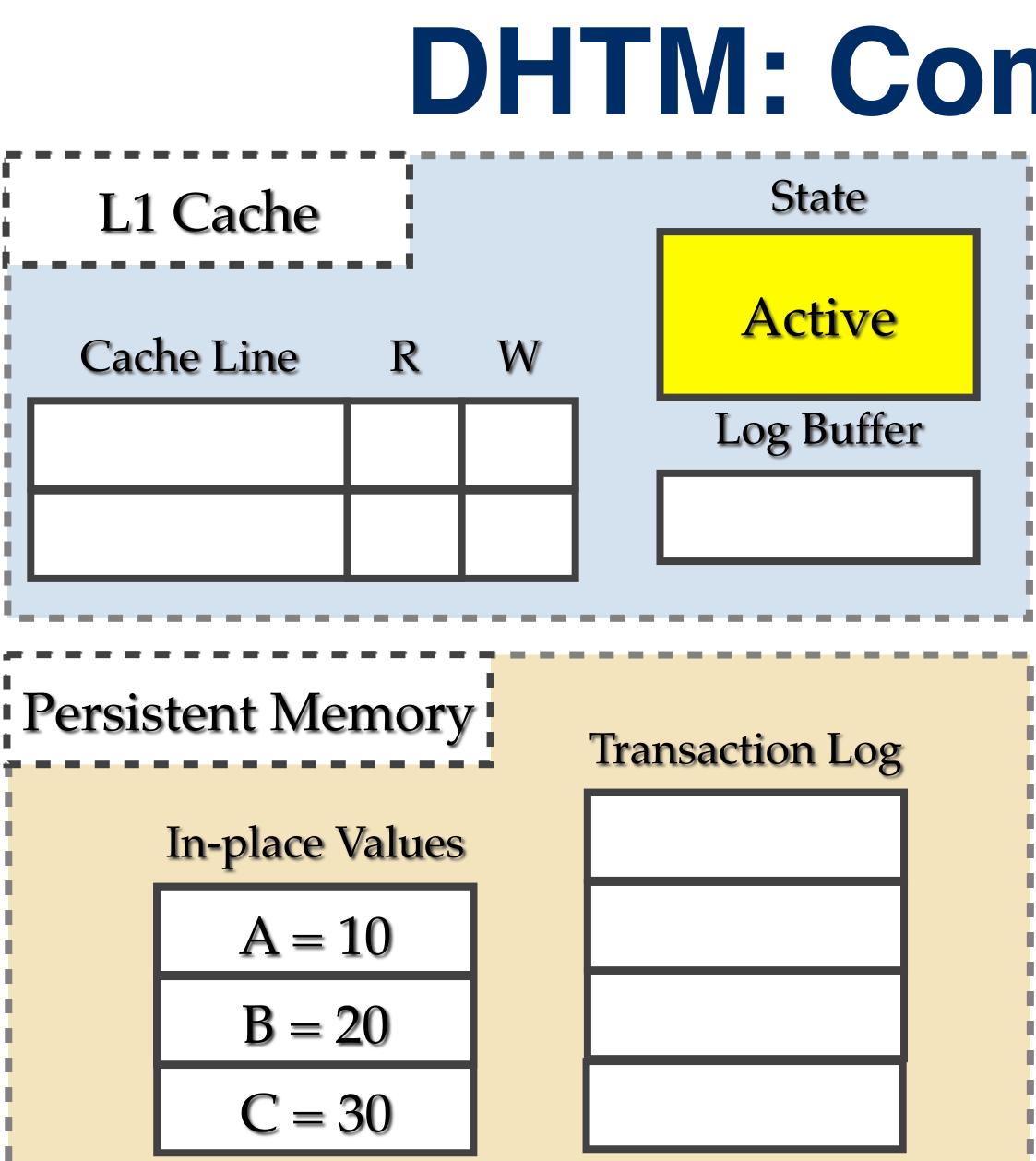

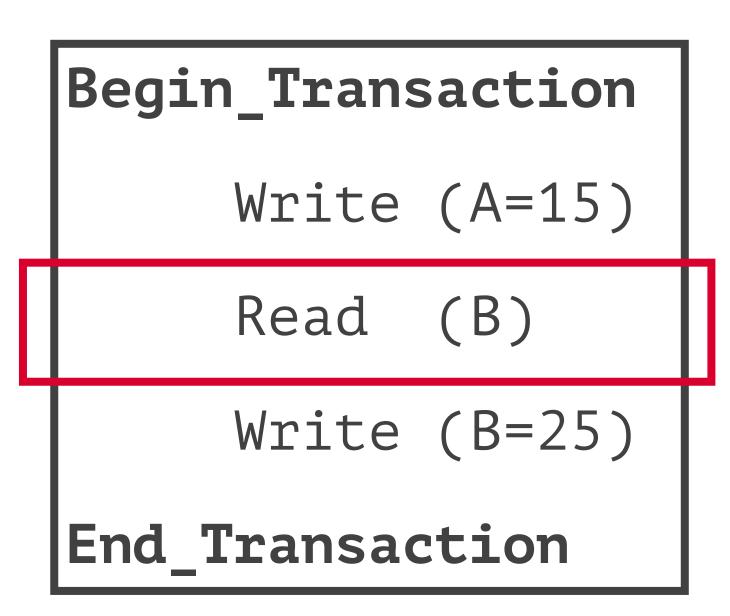

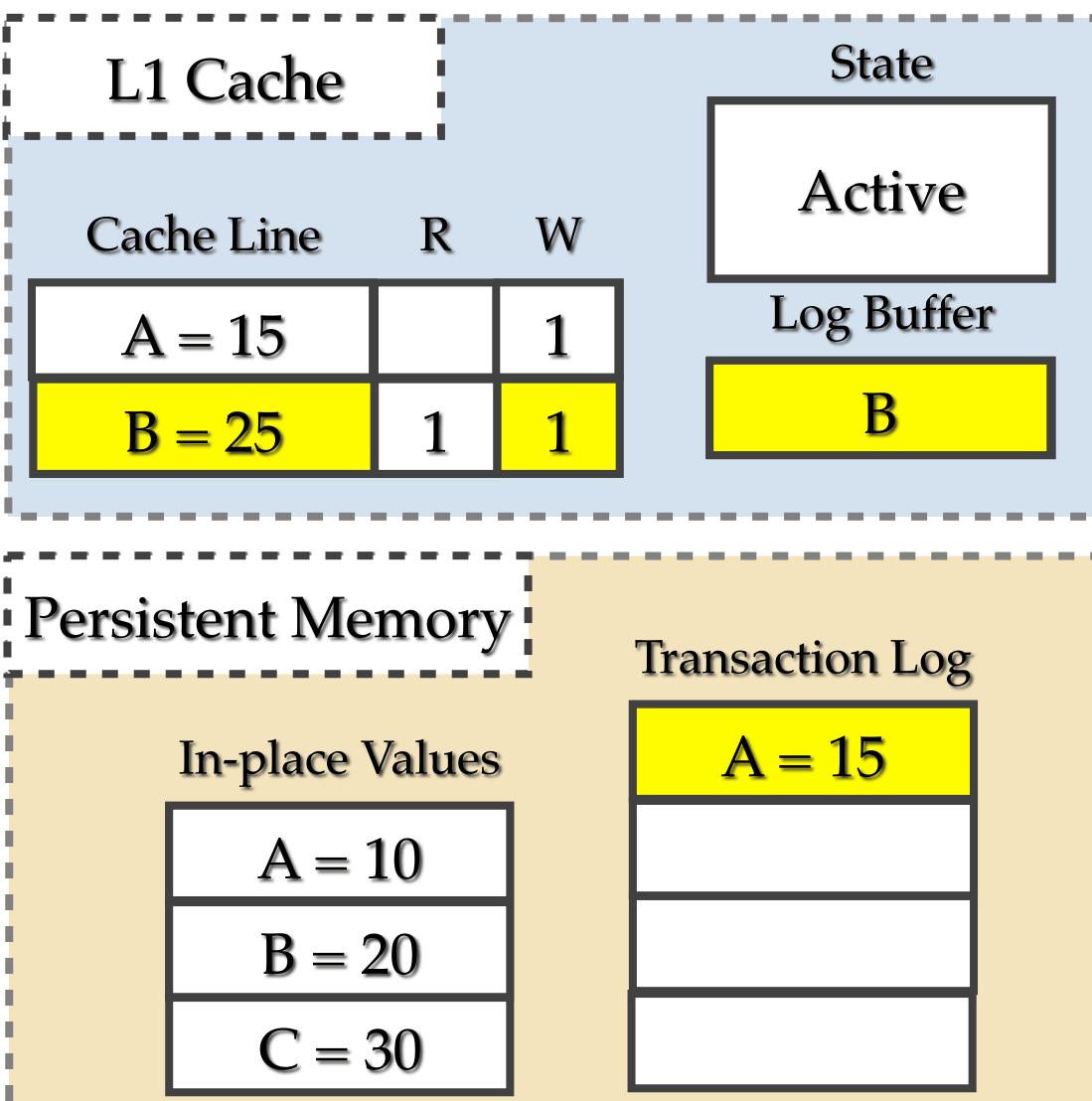

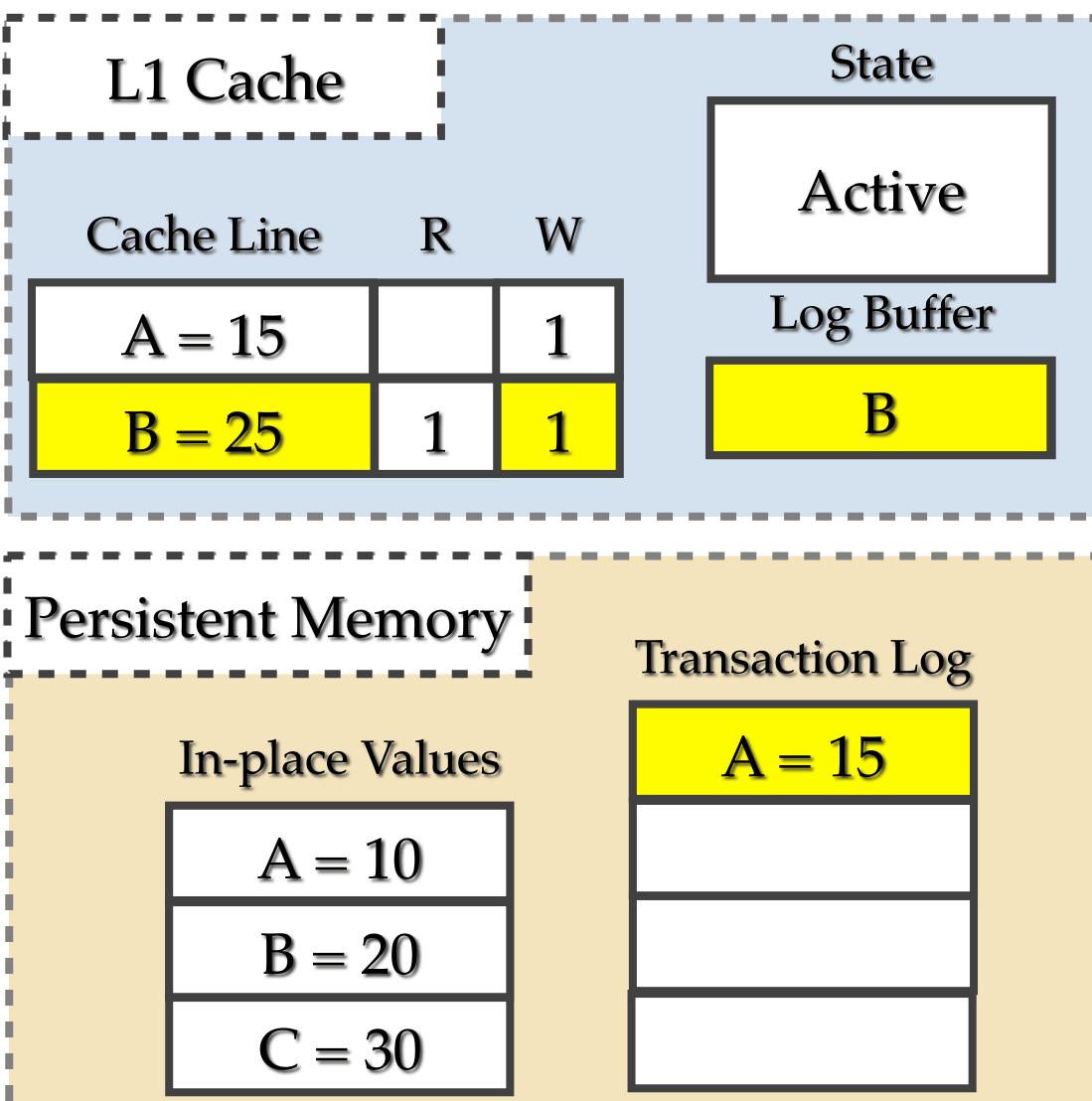

# **DHTM: Commit Example**

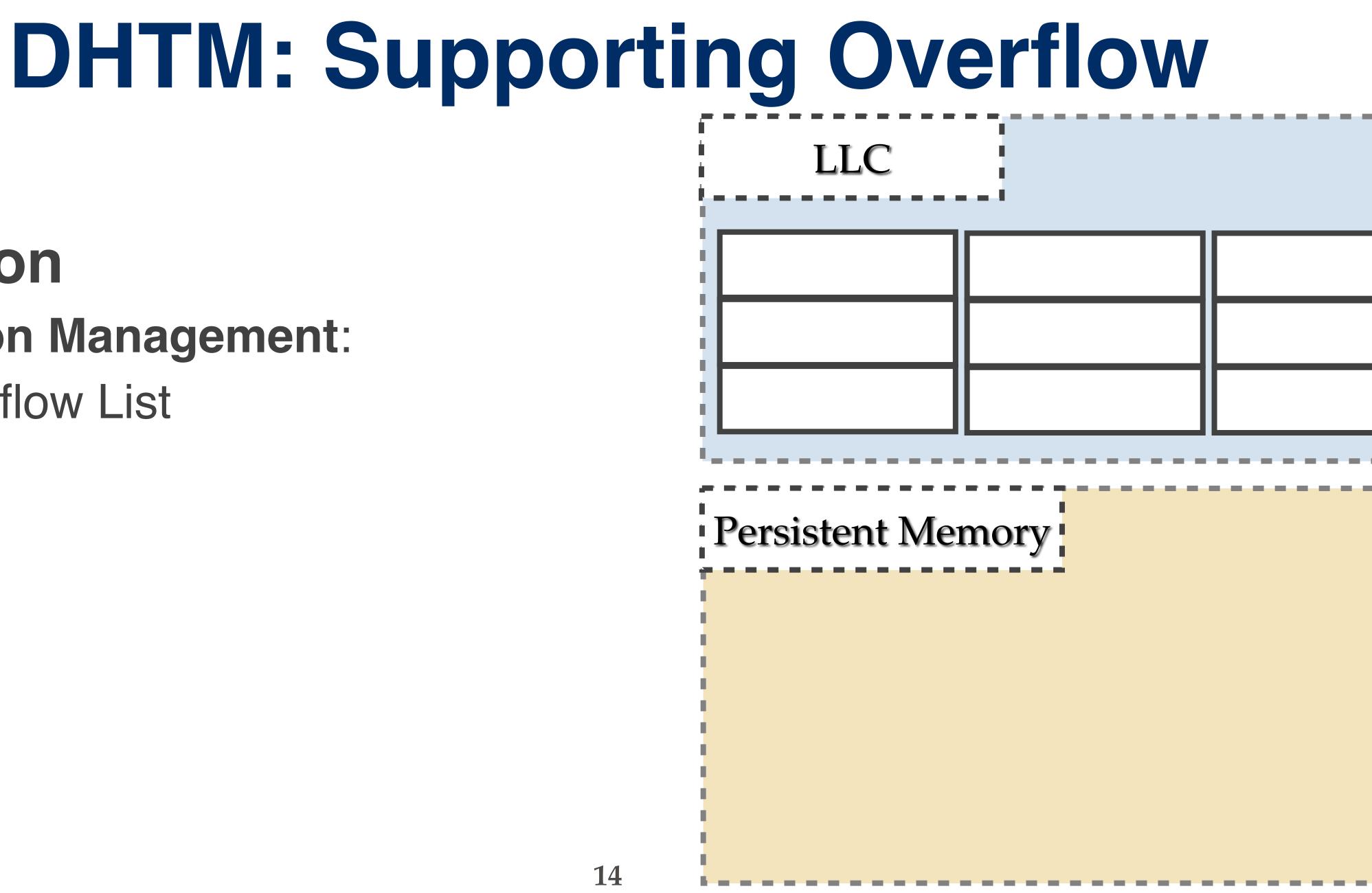

### Begin\_Transaction

Write (A=15)

Read (B)

Write (B=25)

End\_Transaction

# **DHTM: Commit Example**

## Begin\_Transaction

Write (A=15)

Read (B)

Write (B=25)

End\_Transaction

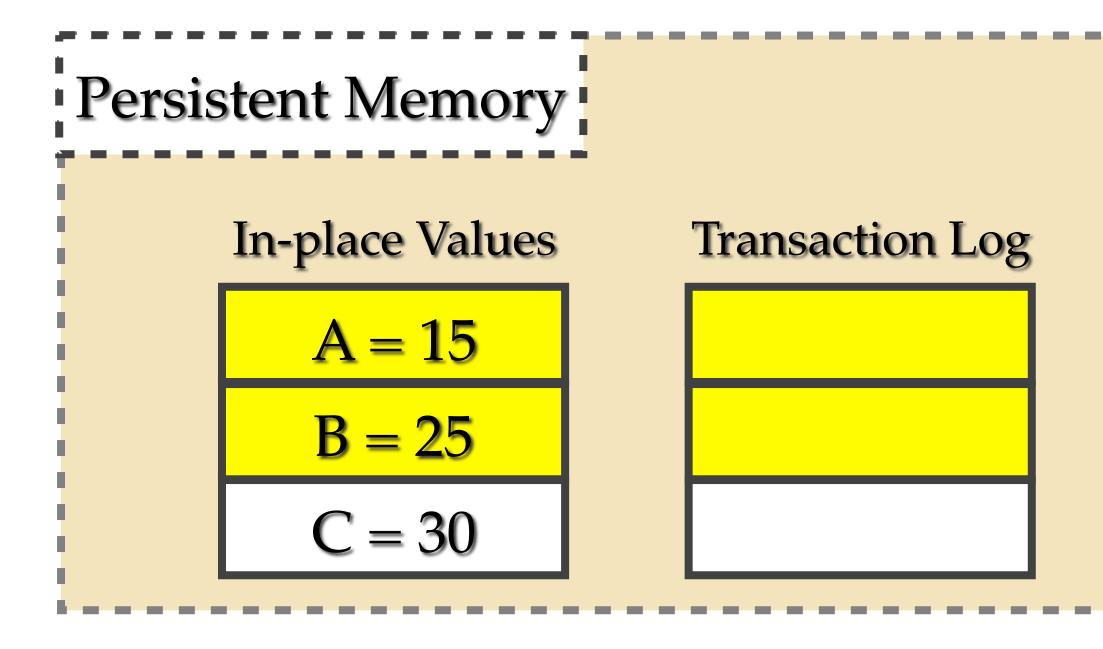

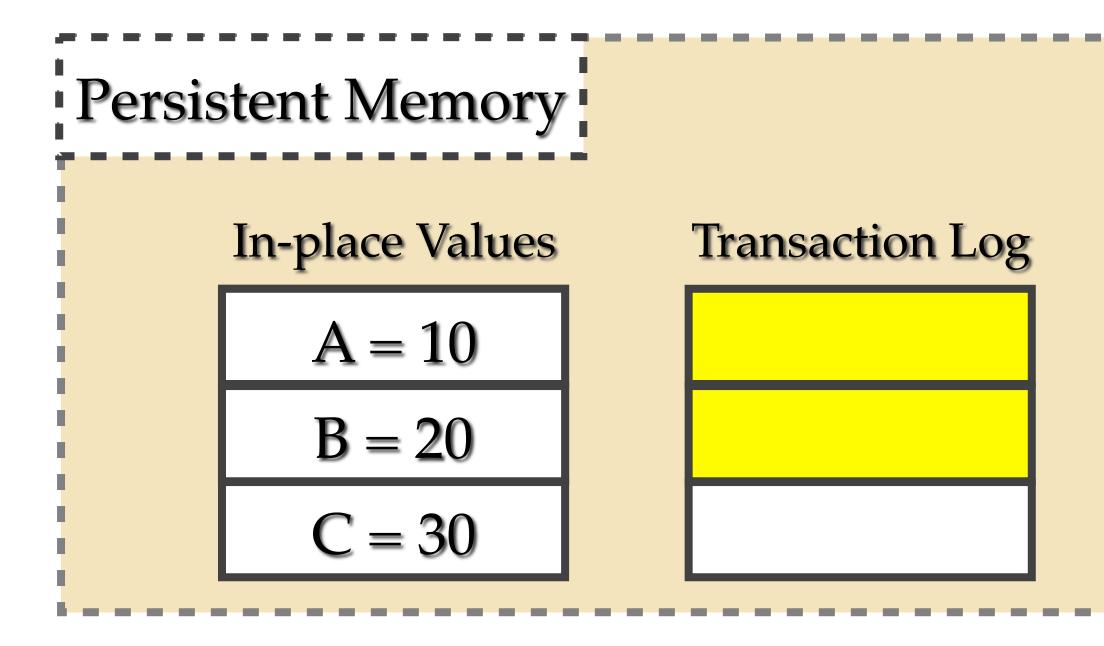

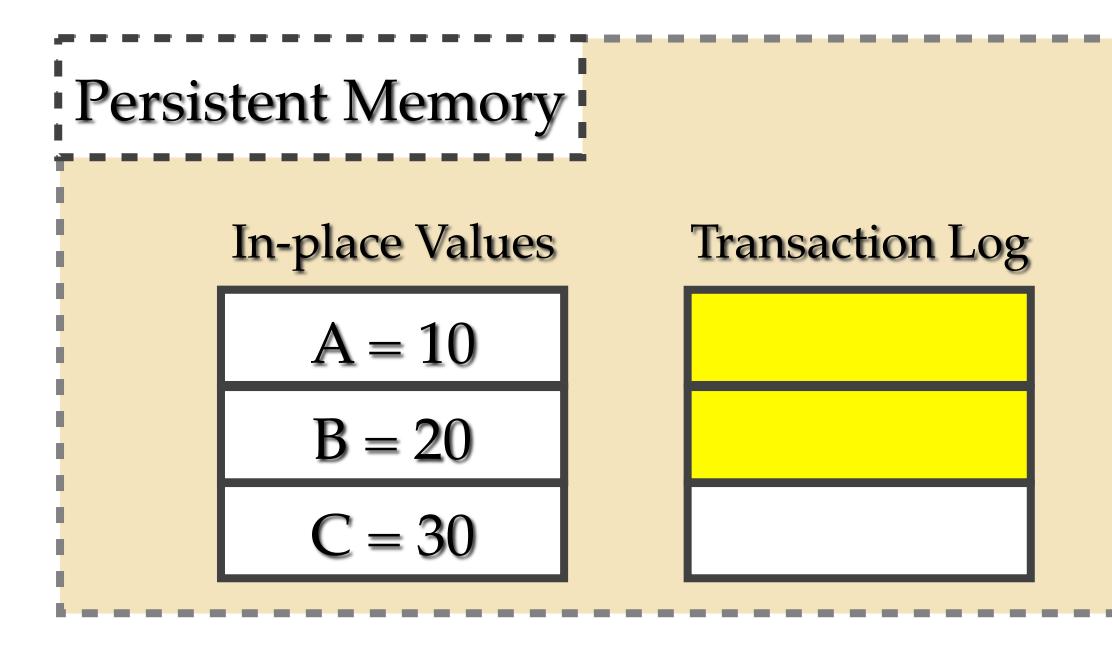

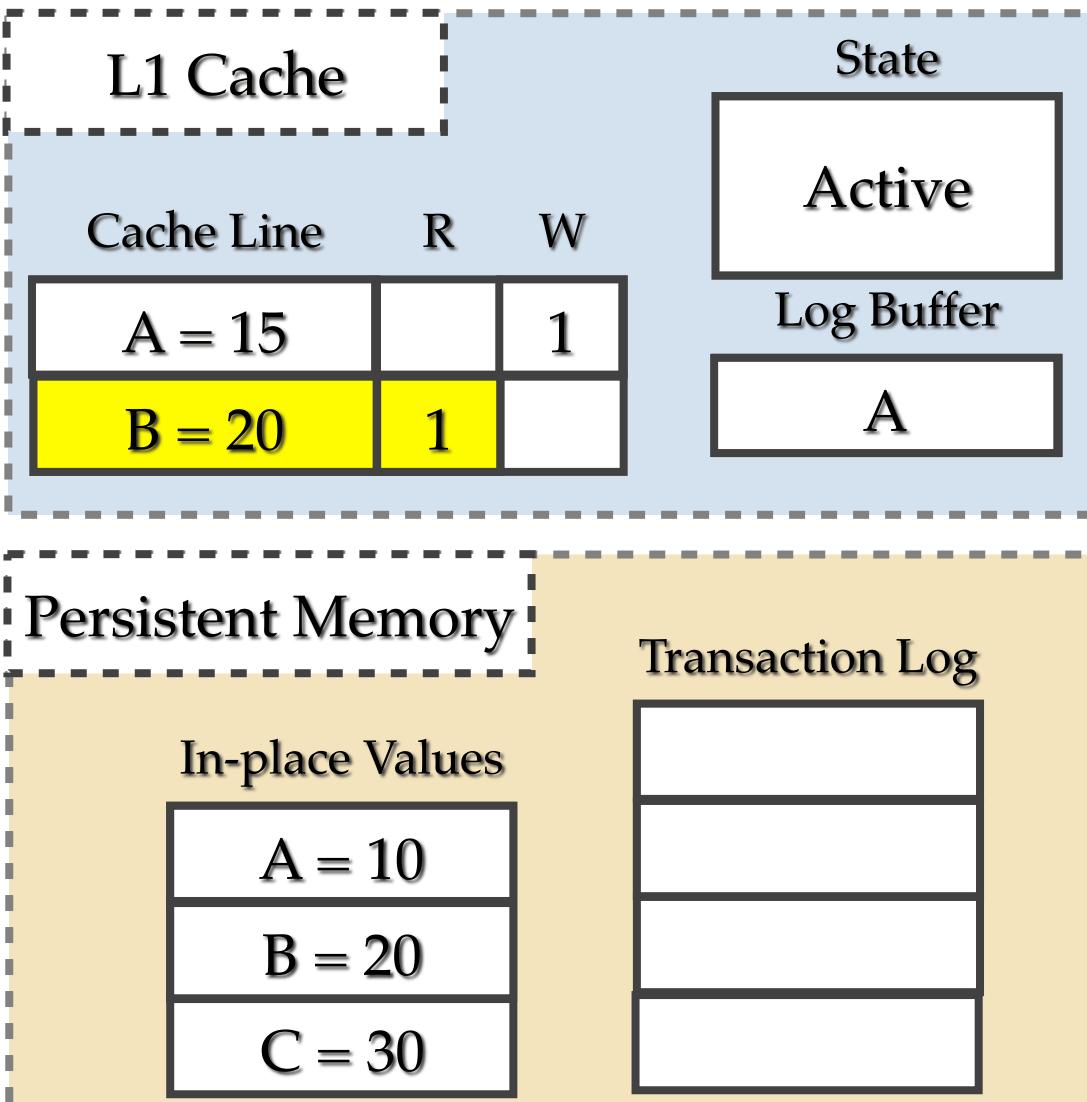

### **DHTM: Commit Example** State L1 Cache Active Cache Line R W Begin\_Transaction Log Buffer A = 15 1 A Write (A=15) Read (B) Persistent Memory **Transaction Log In-place Values** End\_Transaction A = 10B = 20C = 30

# **DHTM: Commit Example**

### **DHTM: Commit Example** State L1 Cache Active Cache Line W R Begin\_Transaction Log Buffer A = 15B Write (A=15) B = 251 Read (B) Persistent Memory Write (B=25) **Transaction Log** A = 15 **In-place Values** End\_Transaction A = 10B = 20C = 30

### **DHTM: Commit Example** State L1 Cache Commit Cache Line W R Begin\_Transaction Log Buffer A = 15Write (A=15) B = 251 Read (B)

Persistent Memory

In-place Values

$$A = 10$$

$B = 20$

$C = 30$

Transaction Log

$$A = 15$$

$B = 25$

Commit

Write (B=25)

End Transaction

# **DHTM: Commit Example**

### Begin\_Transaction

Write (A=15)

Read (B)

Write (B=25)

End\_Transaction

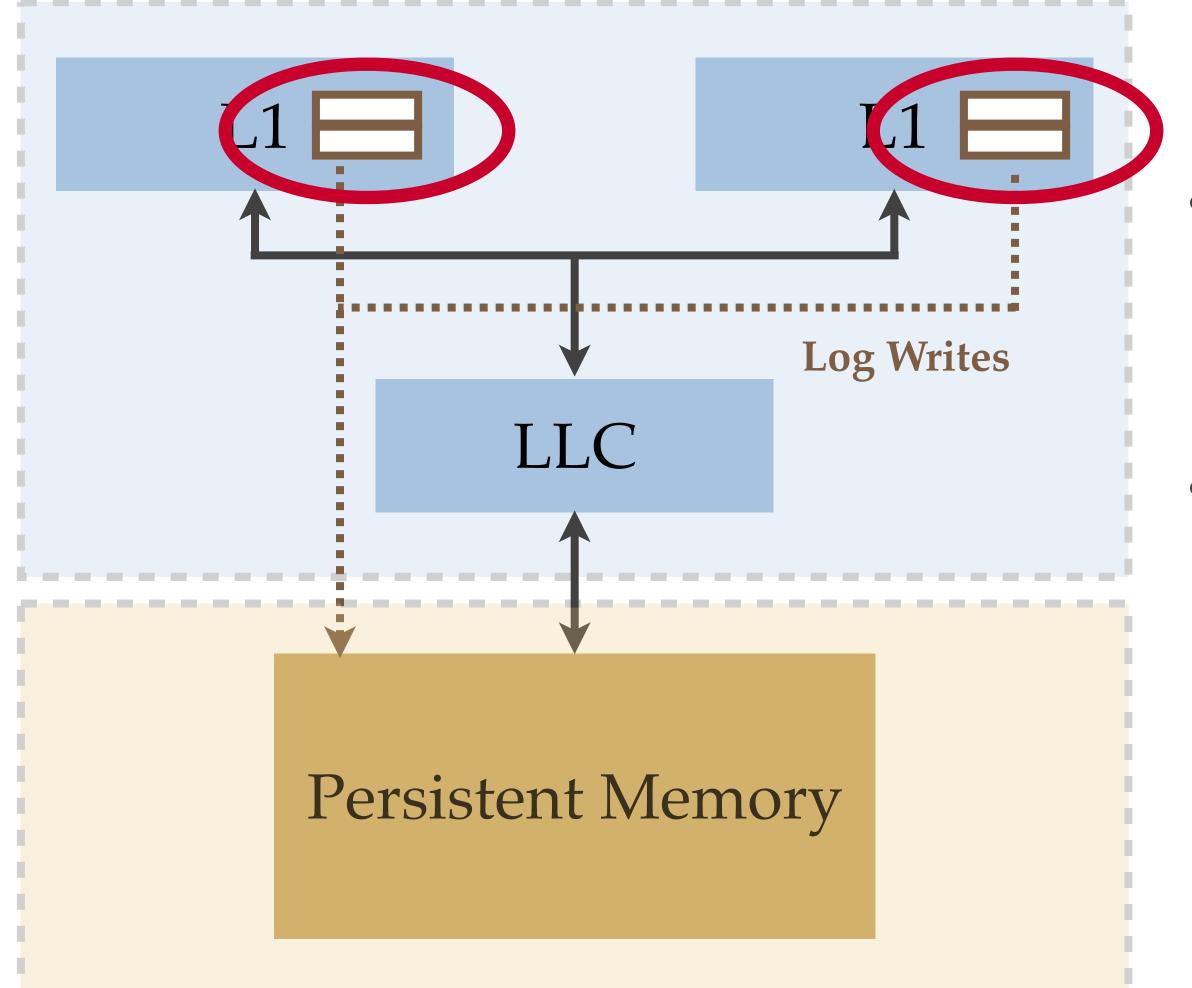

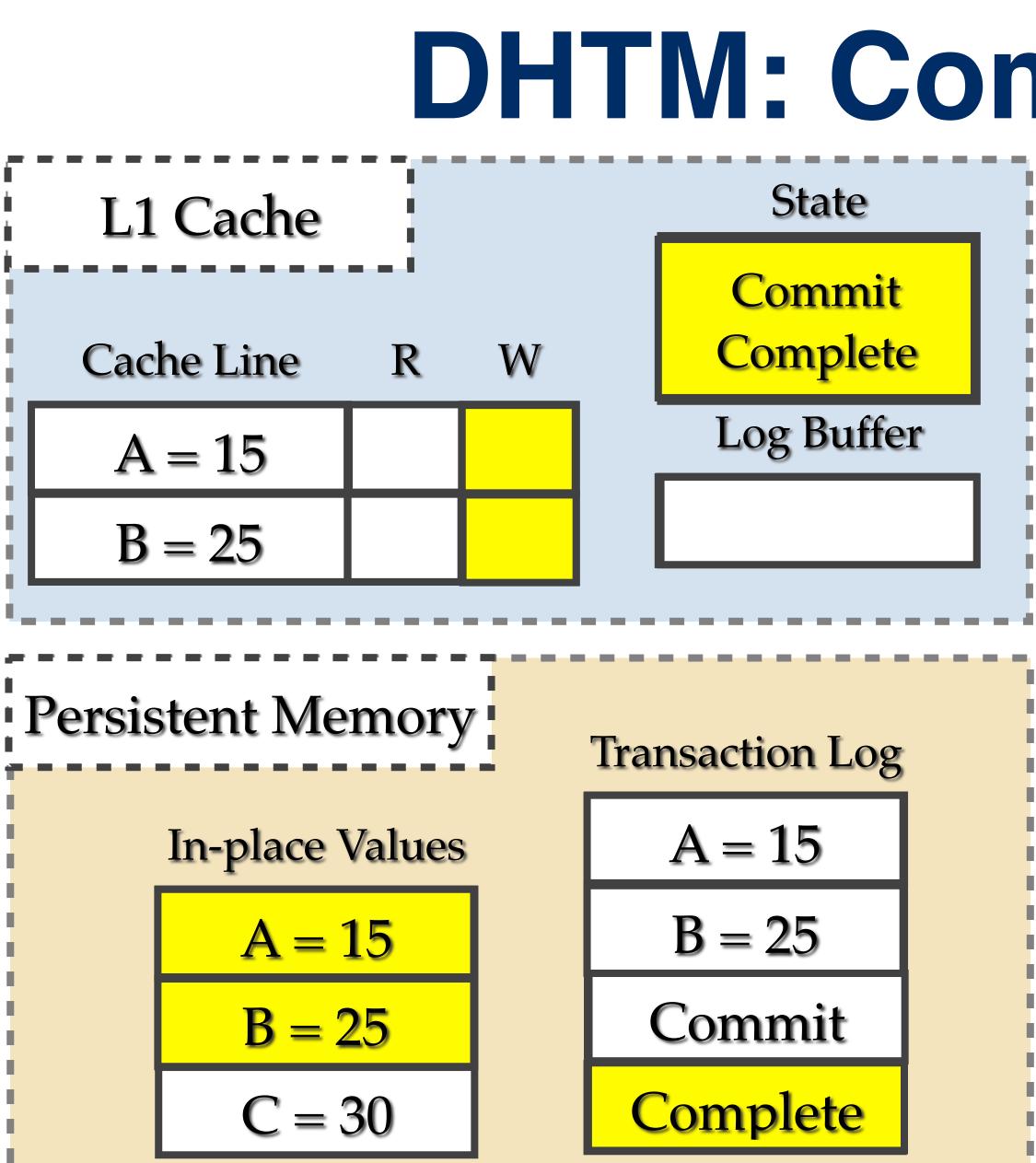

## Problems with Overflow:

- Problems with Overflow:

- Version Management:

- global operation on write-set on a commit/abort

- overhead infeasible in larger caches (beyond L1)

## Problems with Overflow:

- Version Management:

- global operation on write-set on a commit/abort

- overhead infeasible in larger caches (beyond L1)

## - Conflict Detection:

- additional metadata to detect conflicts

- increased complexity due to NACK based protocols

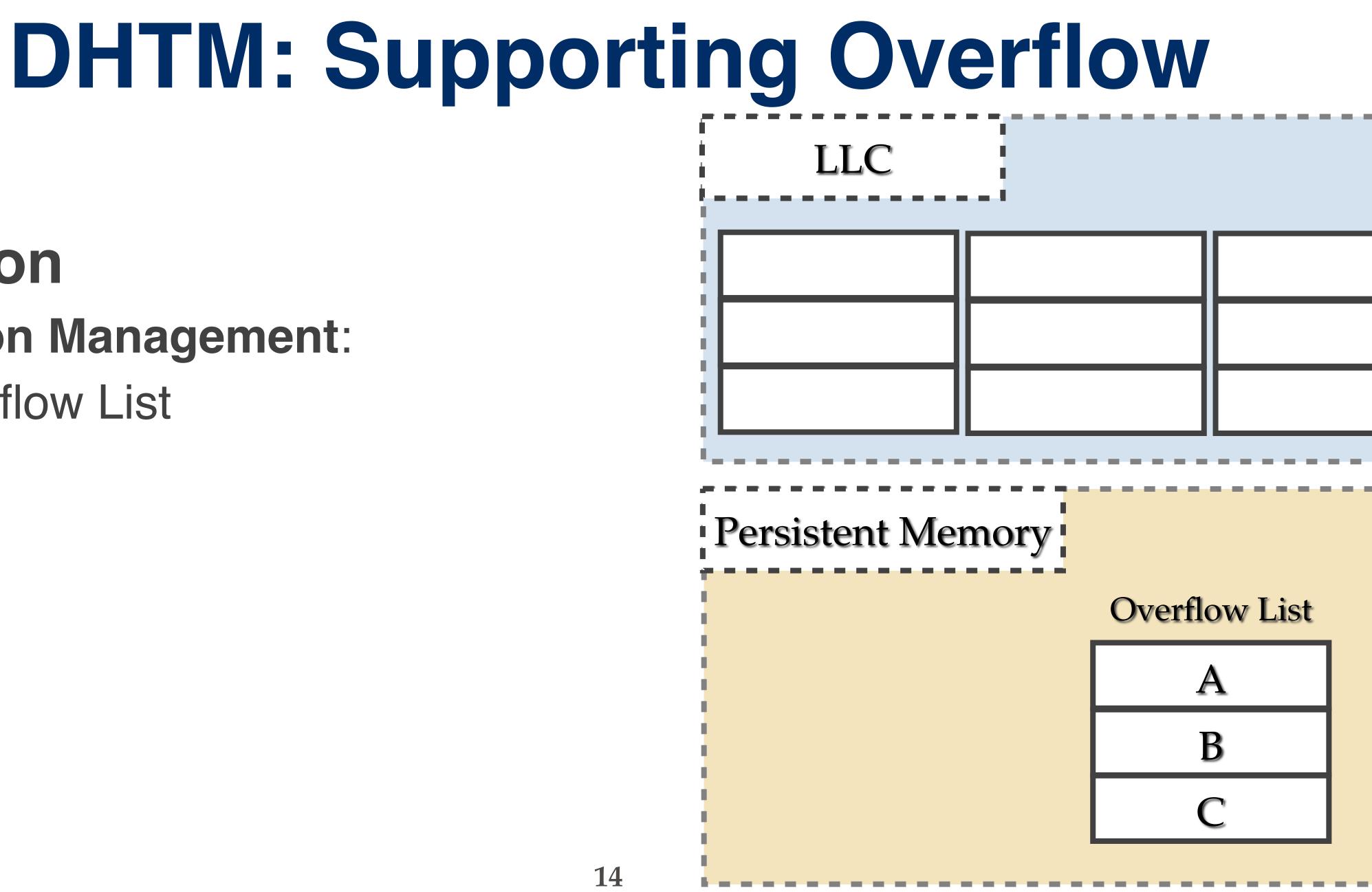

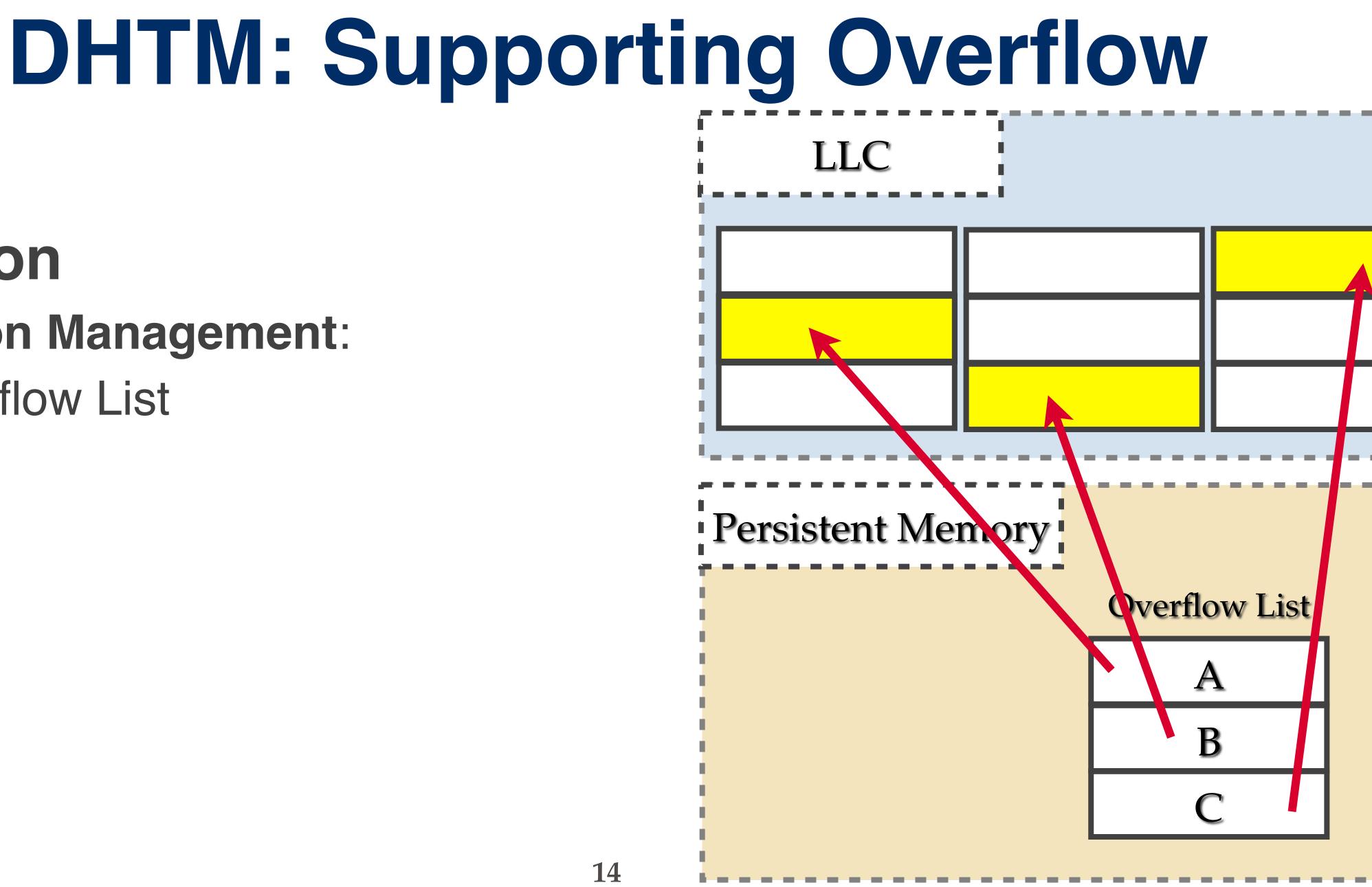

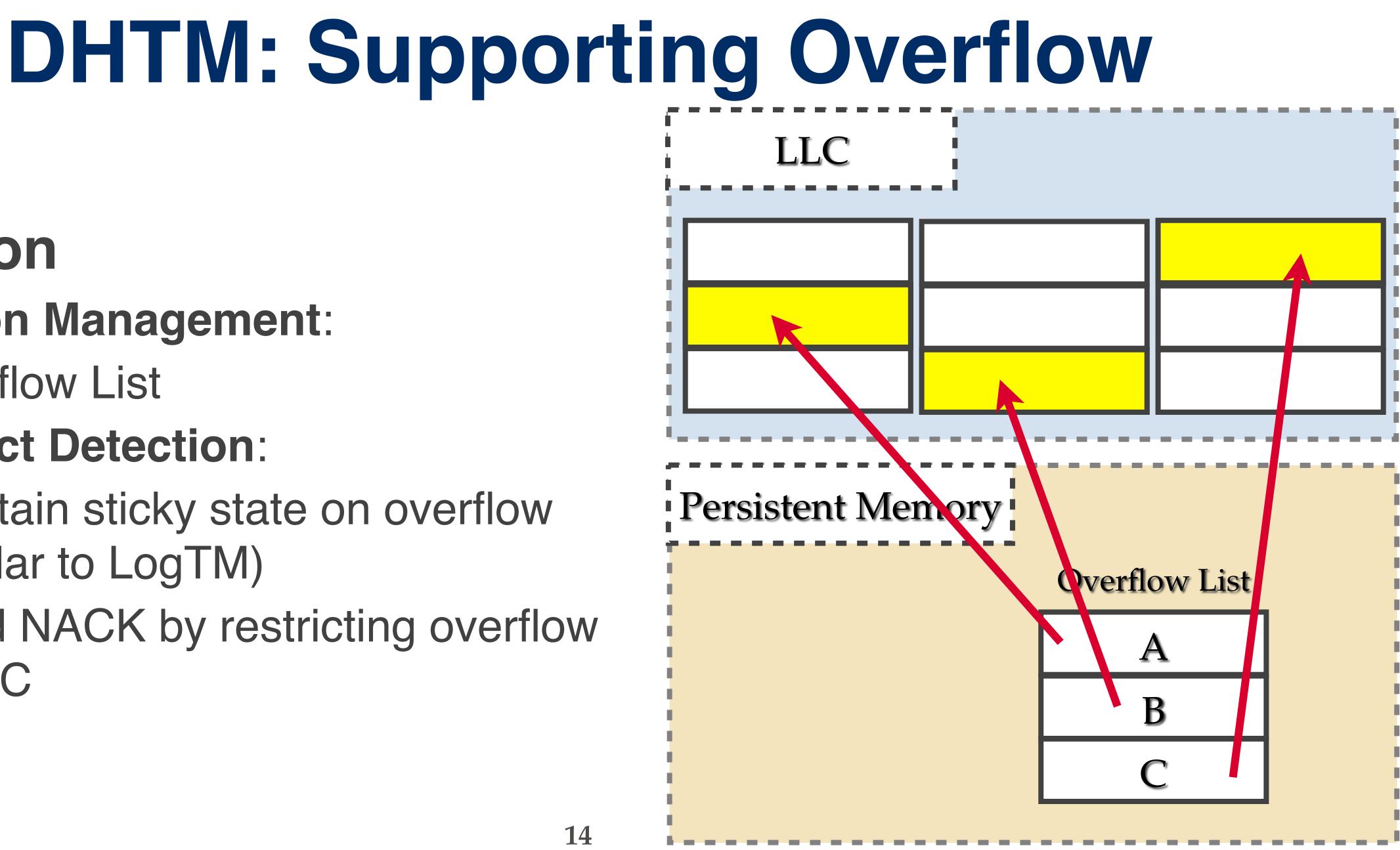

- Version Management:

- Overflow List

- Version Management:

- Overflow List

- Version Management:

- Overflow List

- Version Management:

- Overflow List

- Conflict Detection:

- maintain sticky state on overflow (similar to LogTM)

- avoid NACK by restricting overflow to LLC

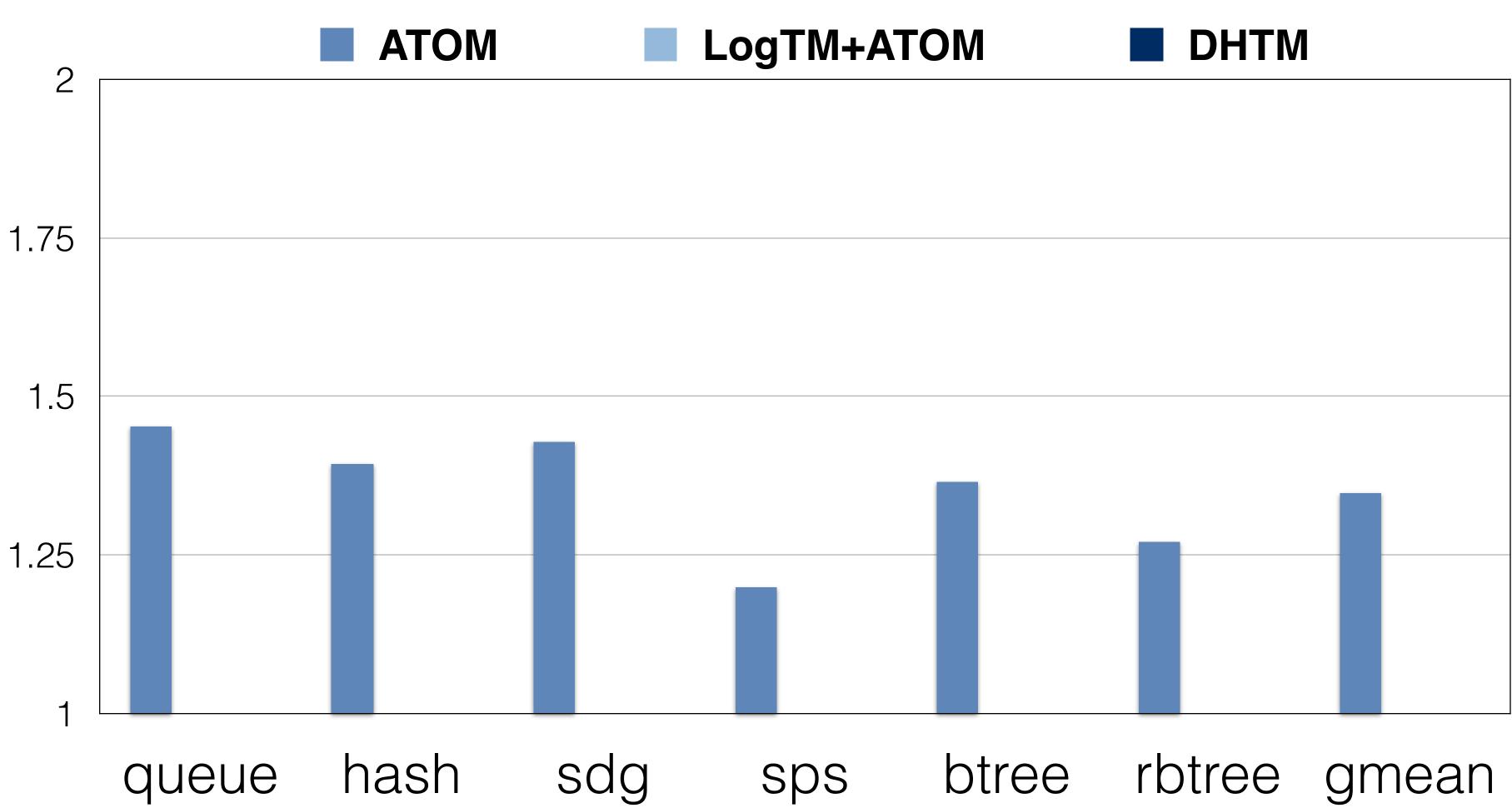

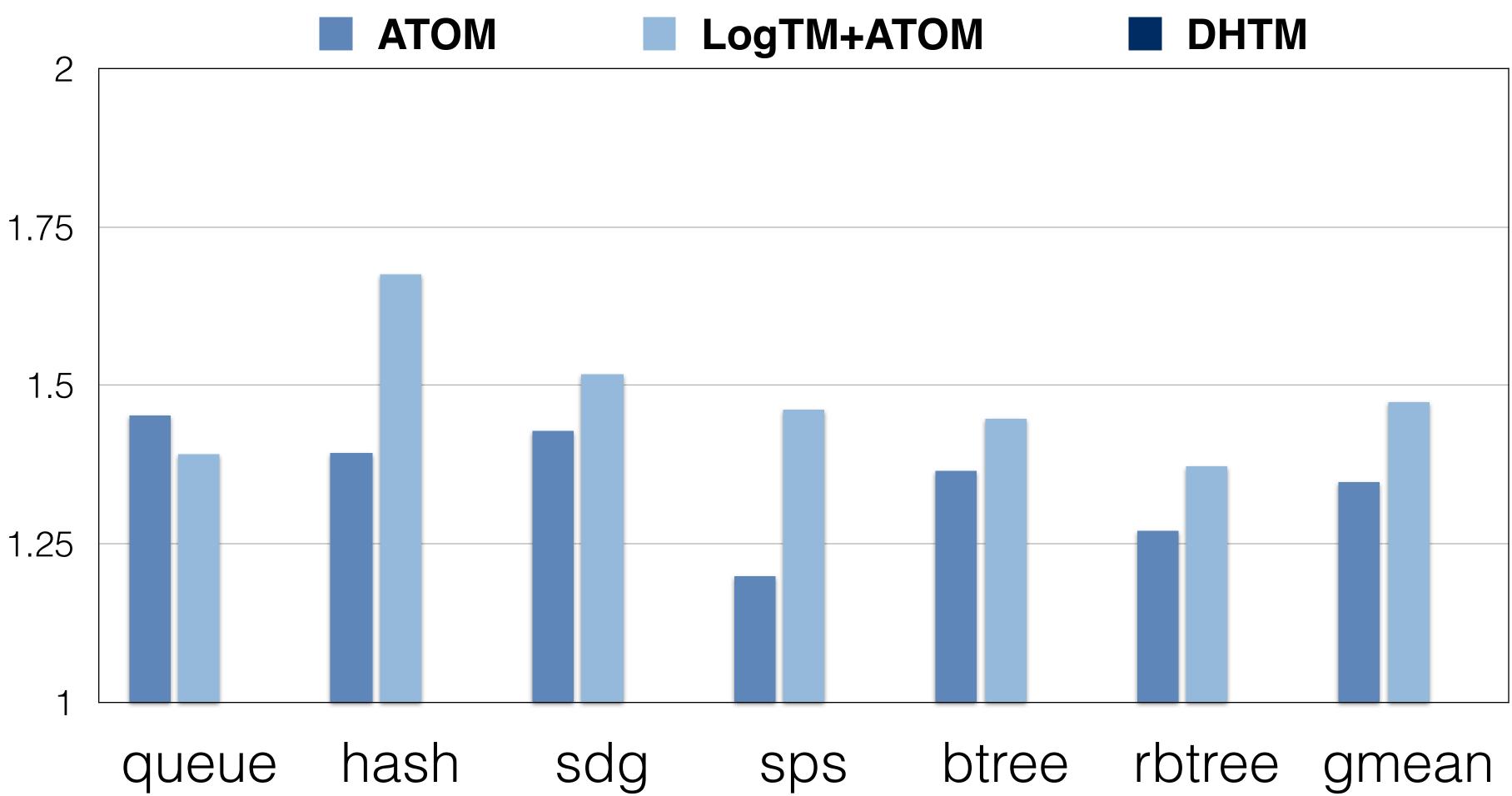

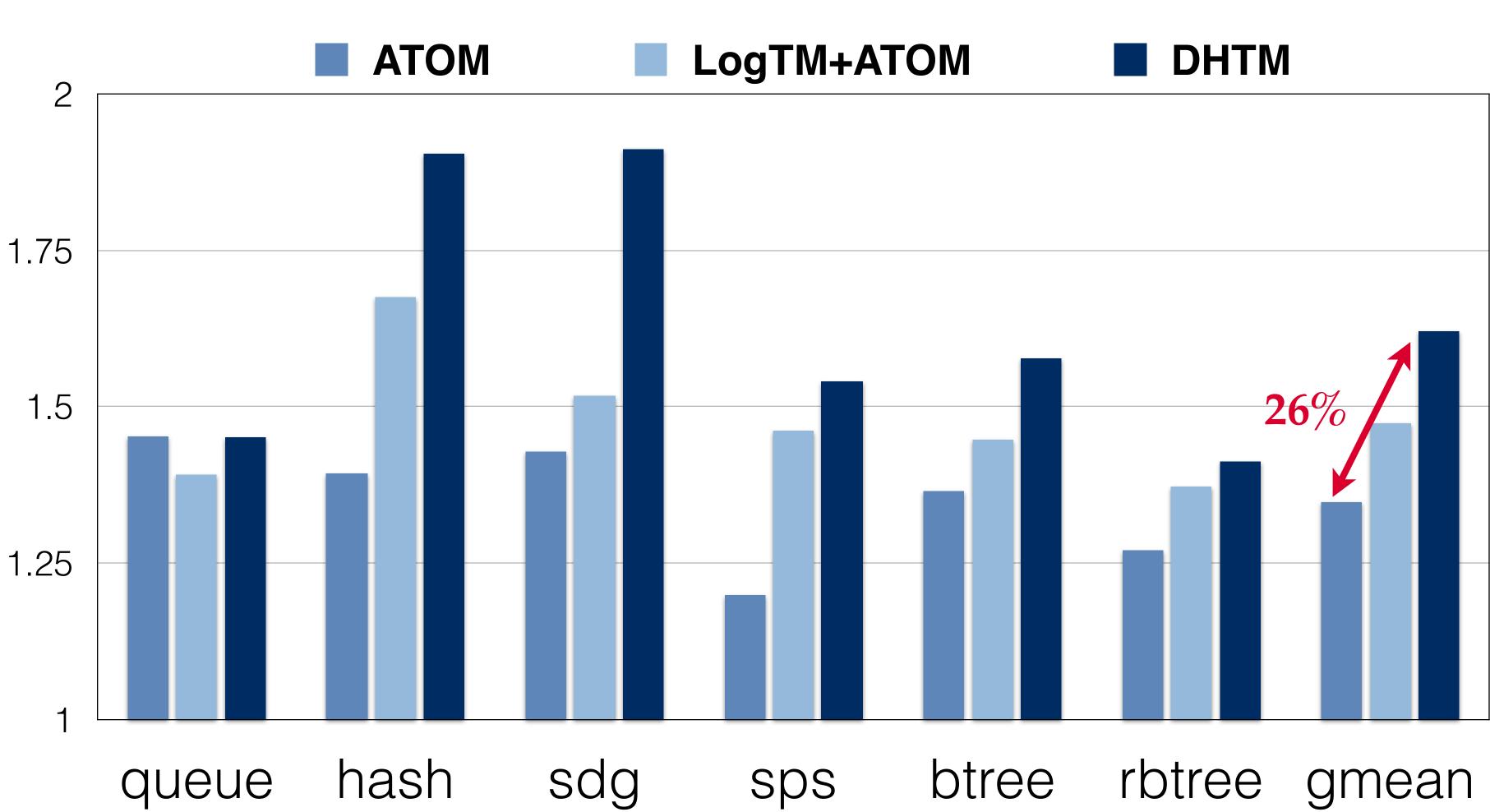

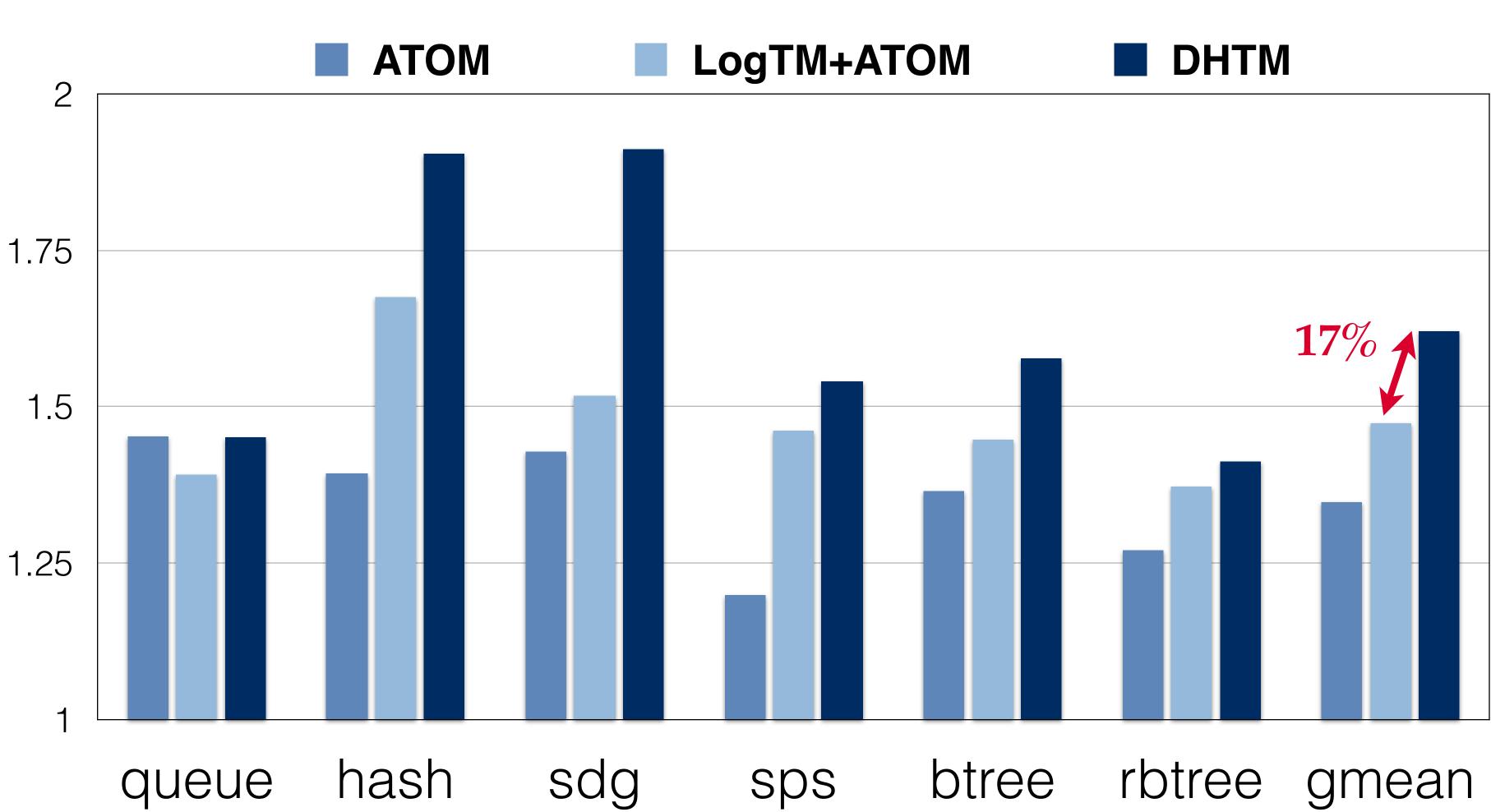

|            | Atomic Visibility | Atomic Durability              |

|------------|-------------------|--------------------------------|

| ATOM       | Locks             | Hardware Undo Log              |

| LogTM+ATOM | HTM (LogTM)       | Hardware Undo Log              |

| DHTM       | HTM               | Hardware Redo Log (Log Buffer) |

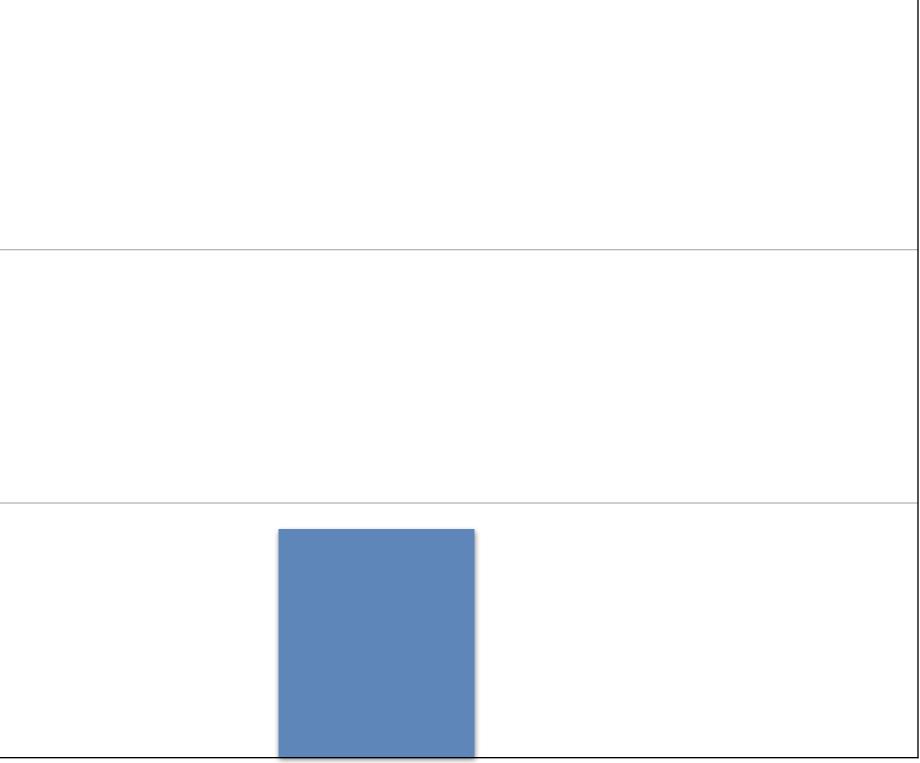

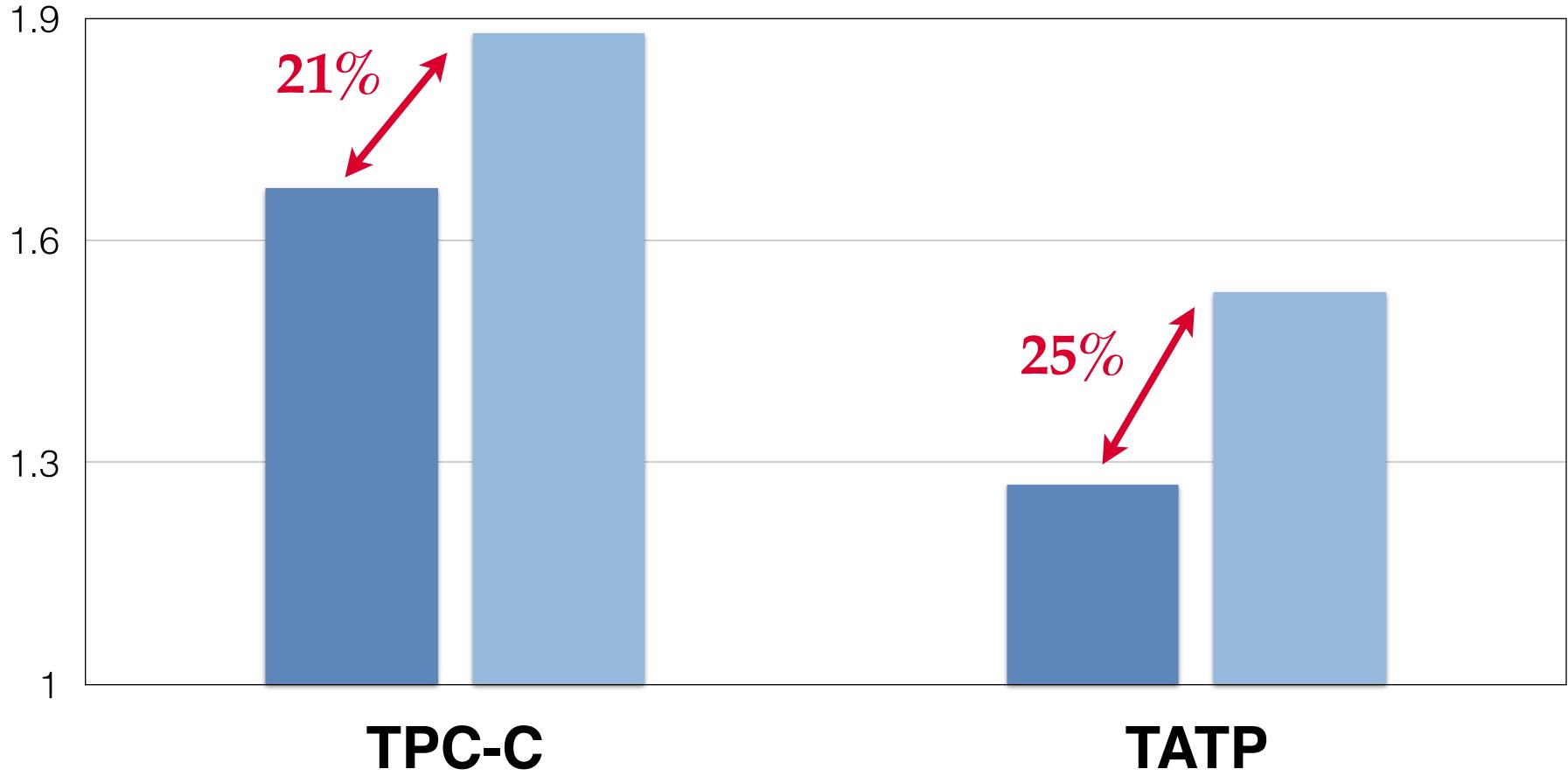

## System Configuration

- HTM's implement (first) writer wins conflict resolution policy

# Evaluation

# - We evaluate an 8-core machine with a 2-level cache hierarchy

# Conclusion

- Persistent memory systems require crash consistency ACID Transactions: widely used crash consistency

- mechanism

- DHTM: ACID transactions in hardware

- Atomic Visibility: commercial HTM

- Atomic Durability: bandwidth optimized hardware redo log

- Leverage hardware logging to extend transaction size unto LLC

# Hardware Support for ACID Transactions in Persistent Memory Systems

## **ARM Research Summit, 2018**

## <u>Arpit Joshi</u>

# CSOInstitute for ComputingSystems Architecture

### DHTM

## TATP

# ATOM 1.9 1.6 1.3 **TPC-C**

# Evaluation

### DHTM

## TATP

### ATOM

### DHTM

### TATP

# Unbounded HTMs

- Do not support atomic durability

- not optimal (eg. LogTM+ATOM)

- Complex NACK based coherence protocols for conflict detection

# - Retrofitting atomic durability to existing mechanisms

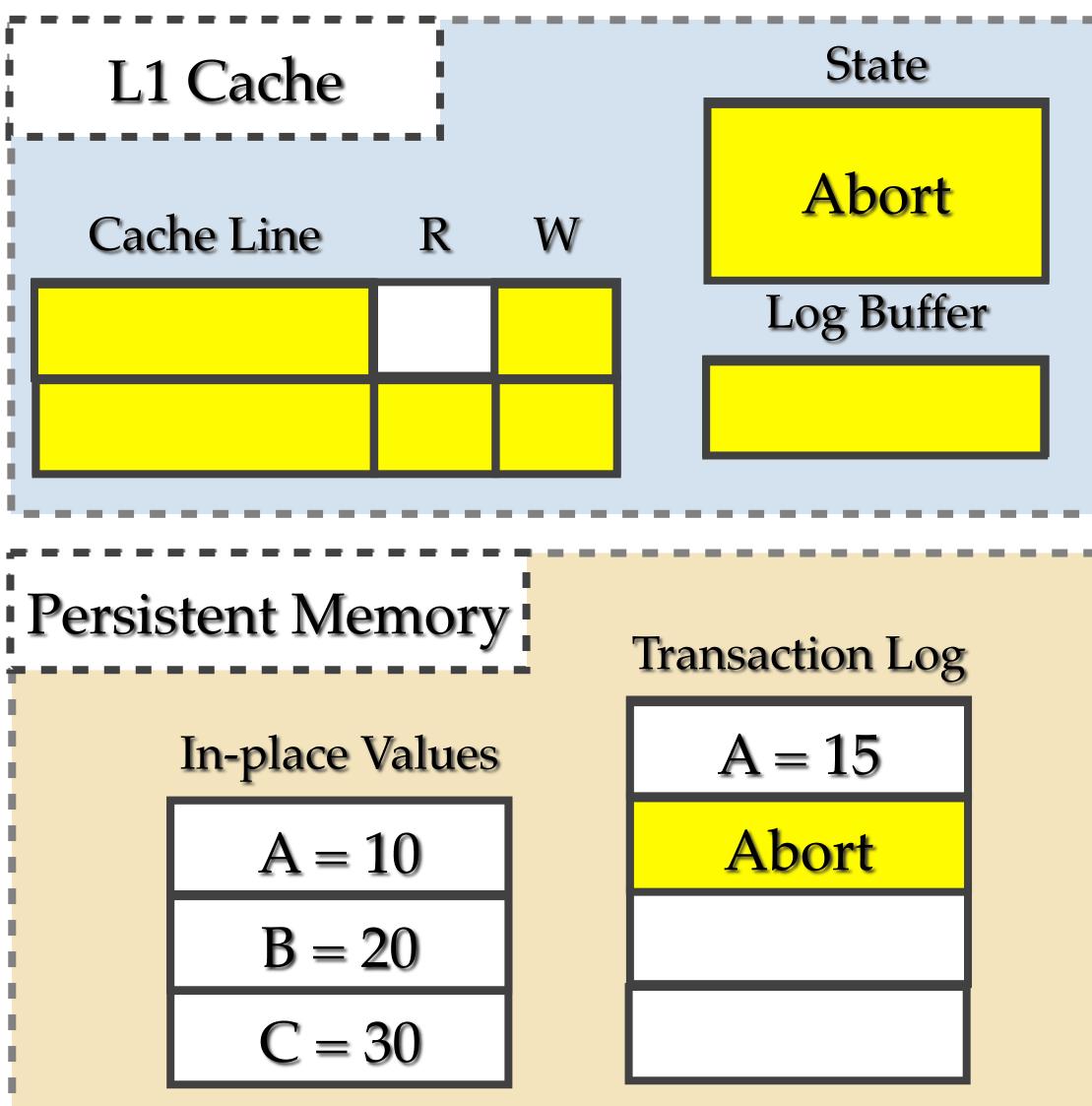

# **DHTM: Abort Example**

### Begin\_Transaction

Write (A=15)

Read (B)

Write (B=25)

End\_Transaction

# **DHTM: Abort Example**

### Begin\_Transaction

Write (A=15)

Read (B)

Write (B=25)

### End\_Transaction

# **DHTM: Abort Example**

# Hardware Support for ACID Transactions in Persistent Memory Systems

## **ARM Research Summit, 2018**

## <u>Arpit Joshi</u>

# CSOInstitute for ComputingSystems Architecture