# VLSI Introduction: Idea to product flow

Mukesh Chopra, Ashish Kumar Sharma

#### Presenters

- Mukesh Chopra Director, Microcontroller & Discrete ICs Group (MDG) R&D India STMicroelectronics

- With 20+ years in semiconductor industry (VLSI & Software), Mukesh has strong Leadership acumen having a rich experience across SOC development cycle including SOC design & verification, Subsystem/IP development, System level design, Design methodology & Foundation library development.

- He has contributed to products ranging from 0.18um to 5nm technologies in consumer, automotive, industrial & storage domains. In addition, he has actively participated in International Standardizing bodies.

- Led several cross-functional and global task forces, driven EDA partnerships to solve complex organizational and technical challenges.

- Ashish Kumar Sharma IP Sourcing MDG GPM IDC, STMicroelectronics

- Ashish is managing IP Sourcing for General Purpose Micro (GPM) products in ST, Greater Noida. With 22+ years of experience, he has experience doing things in verification, design, architecture domain from scratch.

- Has deep expertise in architecture definition, planning, execution, resource management, risk mitigation, strategy loop development and deployment, cross functional working with various stakeholders, customer interaction, managing teams across different sites.

- A recognized leader is a pro on cross vertical coherence, diversity, collaborative leadership and deploying processes to attain reliability-repeatability-consistency and sustainability.

#### Agenda

#### **VLSI Industry overview**

## Semiconductors industry is an industry built on sand

|                                  |                  | the second s |

|----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------|

| Sand                             | • <\$1/Kg        |                                                                                                                |

| Polysilicon                      | • \$50/Kg        |                                                                                                                |

| 200mm Prime Wafer                | • \$1,400/Kg     |                                                                                                                |

| 200mm Processed Wafer            | • \$25,000/Kg    |                                                                                                                |

| Packaged Integrated Circuit      | • \$100,000/Kg   |                                                                                                                |

| Generating End Equipment Worth   | • \$500,000/Kg   |                                                                                                                |

| With A Street Value of More Than | • \$1,000,000/Kg |                                                                                                                |

|                                  |                  |                                                                                                                |

#### Semiconductor and Geopolitics

The Geopolitics Of AI Chips Wil Tech Today Congress: India needs to build an in-house semiconductor supply chain, says panel Define The Future Of AI Geopolitics Uistoriung Cinip Warantee From chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee Analysis Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global Locating Fabs Locally No Guarantee From Chip shortages to global shor on a Chip' at today's Tech Today 🖙 n were extensively deliberated upon during the panel discussion on 'The World Competitive Edge: TMSC CEO On 'D chess: Geopolitical struggles Competitive Edge: TMSC CEO On 'D chess: Geopolitical struggles Taiwanification' Of Semiconductor are reshaping the Japan revamps semiconductor strategy as competition and eightons and tensions in Jar eightens Buffett says geopolitics a factor in Berkshire sale of TSMC stake Industry semiconductor supply chain, says Intel boss **Chiplet Innovation Will Extend Moore's** Law & Emerge As Crucial Component In **US-China Tech Dominance Rivalry**

#### **Applications**

life.augmented

#### Product Type

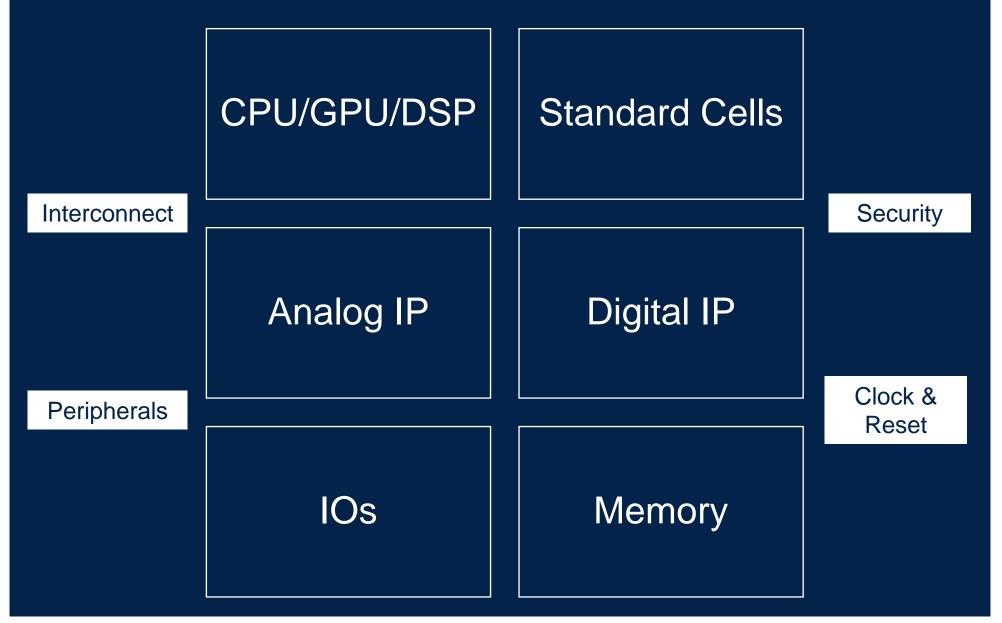

## **Building Blocks**

#### Building blocks of SOC

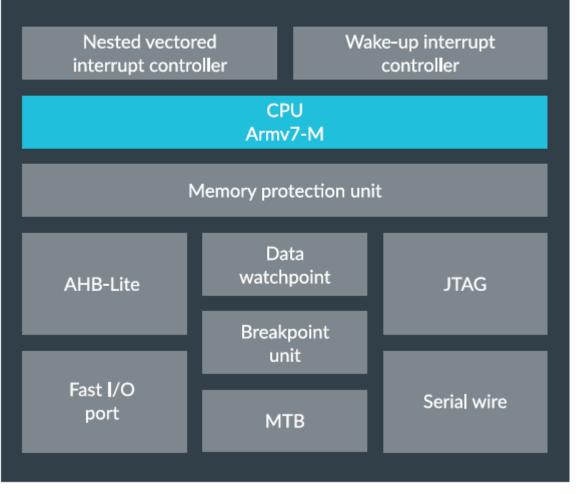

#### Processor

#### **arm** CORTEX®-M0+

- Three-stage pipeline based on a von Neumann bus architecture

- Privilege-level separation

- Memory protection unit

- Small and inexpensive processor

- MTB: Micro Trace Buffer, its low-cost instructiontrace feature

- Optional single-cycle I/O interface for connecting peripherals that need low-latency access

- 32 bit instructions

## Choice between MPU/MCU

| Г   |  |

|-----|--|

| - 2 |  |

|     |  |

| -   |  |

|     |  |

Microcontroller uses on-chip embedded memory (FLASH, PCM, MRAM, ReRAM etc.), to store and execute its program.

Fast but size constraint

Microprocessor uses external memory for program and data storage

Large storage comes at cost

#### Microprocessor vs Microcontroller

| Processor frequency/performance/capabilities   | * * * * | * * *   |

|------------------------------------------------|---------|---------|

| Rich open operating system support             | ****    | *       |

| Security support flexibility                   | ****    | * * *   |

| External memory size/performance               | ****    | **      |

| External mass storage support                  | ****    | * * *   |

| Peripheral set                                 | ****    | ****    |

| Real time predictibility                       | *       | * * * * |

| Boot time                                      | ***     | ****    |

| Wakeup time                                    | *       | * * * * |

| System power consumption                       | ***     | ****    |

| Overall ease of system conception and bring up | **      | * * * * |

#### IP: Integrated circuit Intellectual Property, also known as IP block or IP core

- These are *reusable block of logic*

- Pre-designed and Pre-verified functional blocks

- IP can be Generic or Fixed

- Parameterized to cater wider use cases (flexible design, may not be area optimized) also known as generic IP. CAN, Ethernet, I2C, MIPI, USB, Memory controller etc.

- *Fixed functionality* (area optimized, context specific), SOC specific IPs like Reset and Clock control, power controller

- **Digital**: Standard interface for configuring its register. Ex CAN, ETHERNET, GPU, CPU.

- Analog: crucial for handling real-world signals. (ADC, DAC, SMPS, LDO, Current Mirror, Comparators, OPAMPS)

- **Soft**: Technology agnostic, synthesizable, delivered in RTL form (sometimes netlist, encrypted), provides flexibility and portability.

- Hard: Technology specific, optimized area, optimized timing, usually delivered as a layout database (GDSII) or as a physical design database

- *Hybrid*: combination of hard and soft

- IP helps in

- Time and Cost Savings, Reusability, Quality and Reliability, Focus on Core Competencies

life.augmented

## **Standard Cells**

- Standard cells are pre-designed and pre-characterized building blocks that can be reused to implement different logic functions. They have fixed sizes, shapes, and layouts, and are stored in libraries that can be accessed by automated tools.

- Combinational logic

- Basic Gates: INV, BUFF, NAND, NOR, AND, OR, EXOR

- Multiplexer: MUX, MUX-INV

- Compound Boolean: AND-OR-INV

- Arithmetic Operation: Full Adder, Half Adder

- Sequential logic

- Flipflops

- Latches

- PPA (Power Performance Area)

- Track: 6T, 8T, 9T, 12T, 18T (Speed vs Density)

- Vt: Low Vt, Standard Vt, High Vt (Timing vs Power)

- Channel doping:  $LVT \rightarrow SVT \rightarrow HVT$

- O/P drive current: HVT  $\rightarrow$  SVT  $\rightarrow$  LVT

- Cell Delay: HVT  $\rightarrow$  SVT  $\rightarrow$  LVT

- Cell Leakage: HVT  $\rightarrow$  SVT  $\rightarrow$  LVT

• Library Views: layout, schematic, symbol, abstract, simulation, spice model, hdl

#### Memory

#### Memory: It's a storage entity used to store data

- Uses *electrical*, *magnetic*,

*optical*, *quantum* properties

to store data in form of bits.

- Various parameter decide its selection: speed-access time, storage capacity, power consumption, volatility, endurance, cost per bit, reliability, temp and environment condition, technology compatibility, design constraints.

|                                                                        | Memory  | ]                 |                                                |  |

|------------------------------------------------------------------------|---------|-------------------|------------------------------------------------|--|

| Nonvolatile                                                            |         | Vol               | atile                                          |  |

| ROM: Read Only Memory                                                  |         | RAM: Random A     | ccess Memory                                   |  |

| PROM: Programmable ROM                                                 |         | Asynchronous      | Synchronous to Clk                             |  |

| EPROM: Erasable PROM                                                   | Static  | SRAM: Static RAM  | SSRAM: Synchronous SRAM                        |  |

| Flash EPROM:<br>Block Erasable/Programmable EPROM                      |         | DRAM: Dynamic RAM | SDRAM: Synchronous DRAM                        |  |

| E <sup>2</sup> PROM: Electrically EPROM                                |         |                   | DDR, DDR2, DDR3, DDR4:<br>Dual Data Rate SDRAM |  |

| FRAM: Ferroelectric RAM                                                | Dynamic |                   | GDDR:<br>Graphical DDR                         |  |

| FRAM: Ferroelectric RAM     WY AND |         |                   | LPDDR:<br>Low-Power DDR                        |  |

| PRAM: Phase-change RAM                                                 |         |                   | QDR: Quad Data Rate                            |  |

| FeFET: Ferroelectric FET                                               |         |                   |                                                |  |

## IO, Bumps, Package

- IO refers to the interface or communication between the integrated circuit (IC) and the external world.

- IO pads or cells are located on the periphery of the IC and serve as physical connections between chip and external world. Drive large capacitance off chip

- Operate at compatible voltage levels. Provide adequate bandwidth

- Limit slew rates to control di/dt noise. Protect chip against electrostatic discharge.

- Types of IO can be Vdd/Gnd, Output, Input, Bidirectional, Analog

#### BUMPS

|O|

- Bumps, also known as solder bumps or micro-bumps, are small metallic connections placed on the surface of the IO pads of the chip.

- These bumps are typically made of materials like solder or copper.

- Their primary purpose is to facilitate the electrical and mechanical connection between the chip and the package.

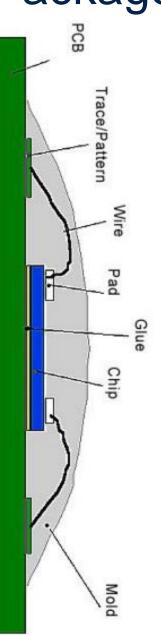

#### Package

- The package, also called the semiconductor package, is the protective casing that houses the IC and provides electrical connections to the outside world.

- The package serves several essential functions, such as protecting the chip from physical damage, dissipating heat, and providing a standardized interface for connecting the chip to external devices or a printed circuit board (PCB).

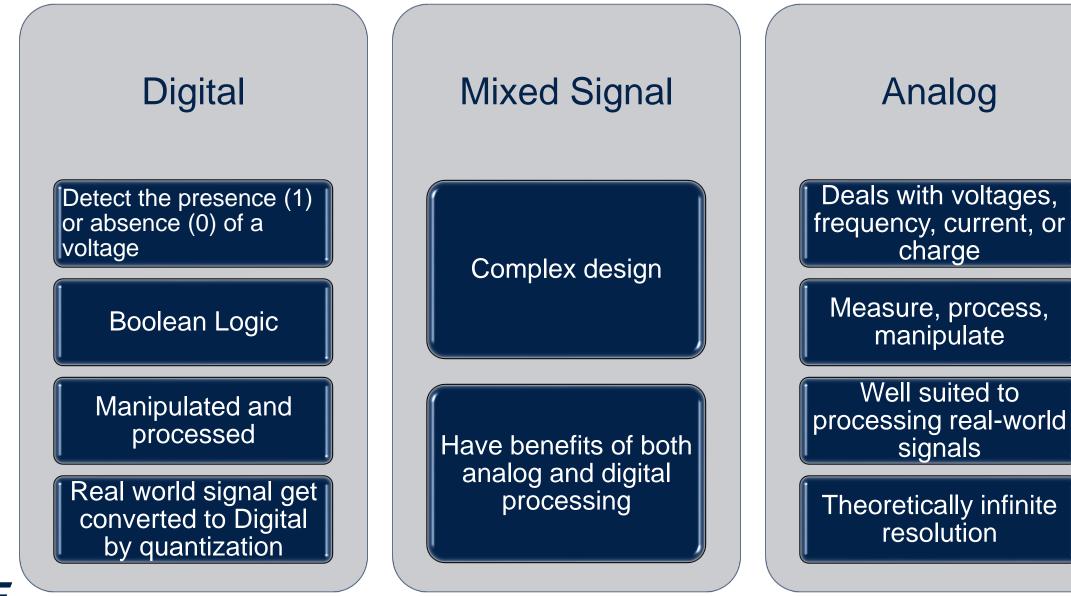

#### Analog on TOP (AOT)

- Designed to work with continuous signals, such as sound, light, or temperature. Can measure, amplify, filter, and process continuous signals. Can process signals with high fidelity

- Require high precision in their design and manufacturing to minimize signal distortion and noise

- Can operate at lower frequencies and with lower voltages than digital circuits. Consume less power and generate less heat

- More complex to design and manufacture than digital circuits, sensitive to temperature changes, noise, and interference.

- Less flexible than digital circuits, as they can only process continuous signals and cannot perform logical operations.

- They typically use components such as resistors, capacitors, and inductors to manipulate these signals.

- Examples: amplifiers, filters, oscillators, and voltage regulators.

## **Type of Integrated Circuits**

#### Digital on TOP (DOT)

- Designed to work with digital signals, which can only have two states, typically represented as 0 or 1

- Digital signals are discrete and have specific voltage levels that correspond to each state

- Can process and manipulate these signals using logic gates and flip-flops, which are components that can store and manipulate digital signals

- Can perform logical operations on digital signals, which makes them suitable for a wide range of applications, from simple calculators to complex computer systems.

- Can also be easily reprogrammed to perform different tasks.

- Less sensitive to noise and interference. Less susceptible to analog effects due to discrete nature

- Consume more power, require higher voltages and operate at higher frequencies.

- Less accurate can introduce errors and noise in the digital signal.

- Examples: microprocessors, memory chips, and digital signal processors

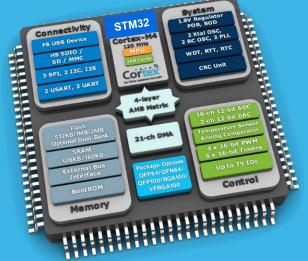

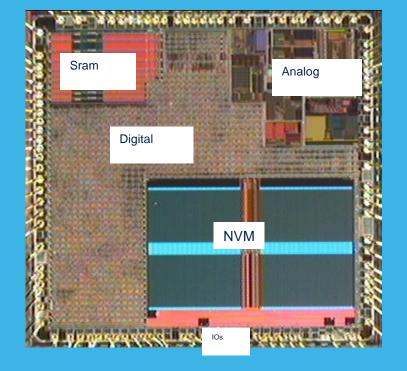

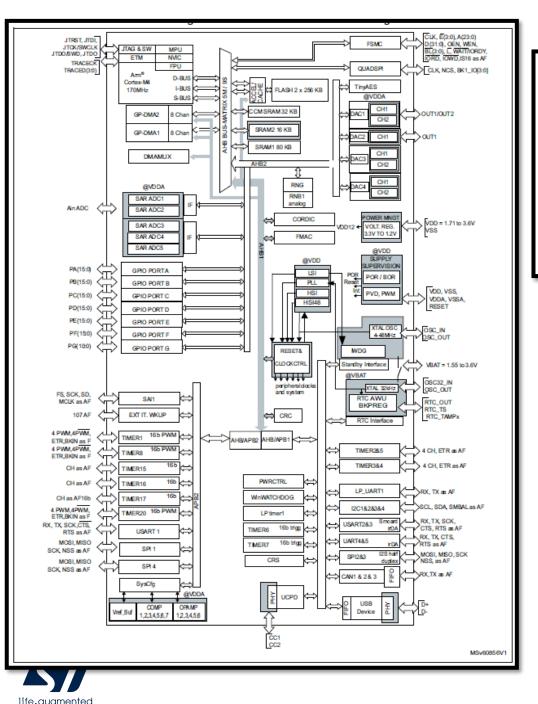

## Microcontroller SOC

#### •ARM Cortex M CPU

- •NVM for Code Storage

- •SRAM

- Digital peripherals

- Analog Ips

- •los

#### Designed in eNVM technology

#### SOC

life.augmented

#### **FPGA**

A field-programmable gate array (FPGA) is an integrated circuit development of the be configured after the second s

pro

hier inter

wired config combin logic ga FPGAs, and XOR. In most FPGAs, and XOR. In most FPGAs, and the simple flip-flops or more complete blocks of memory.

# ASIC

- When a SOC is Application specific it becomes ASIC

- It can have a processor depending on approximation

- Optimized

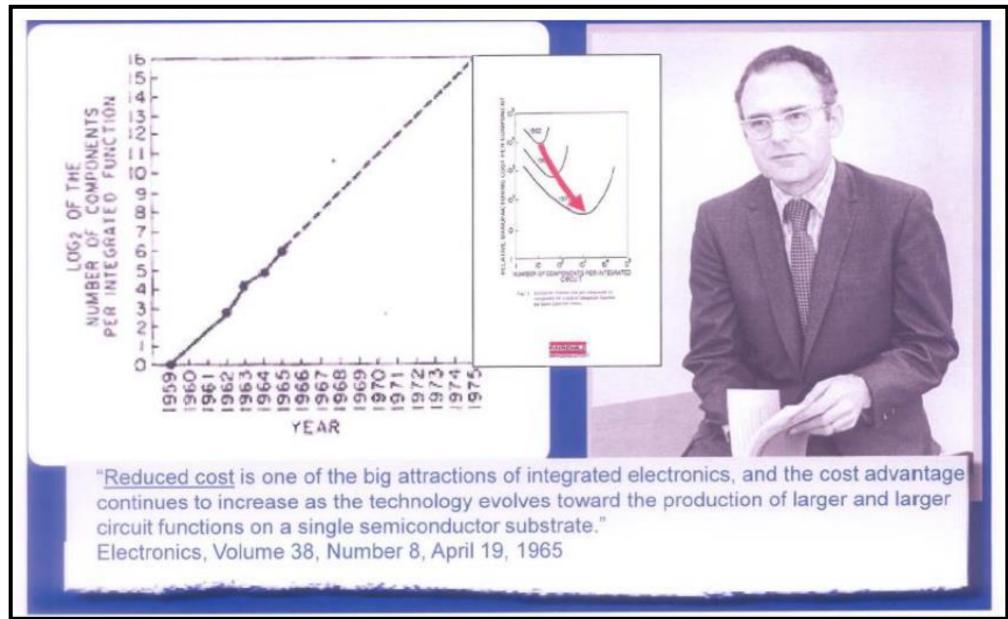

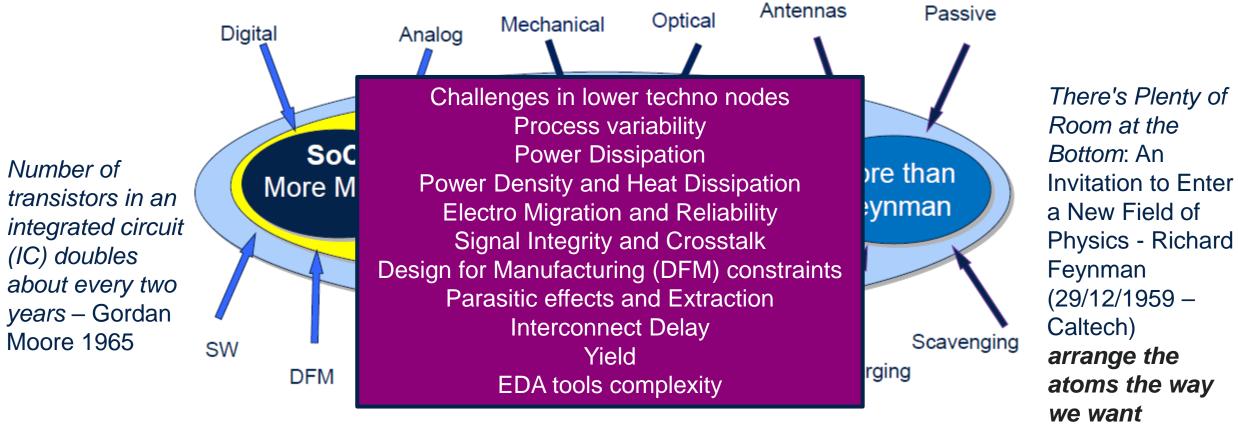

## **Beyond Moor's**

#### Moor's Law - 1965

## **Technology Evolution**

SoC: System on Chip SiP: System in Package MiP: Module in Package

life, gugmented

**Courtesy: Bruno Murari, Scientific Advisor, STMicroelectronics**

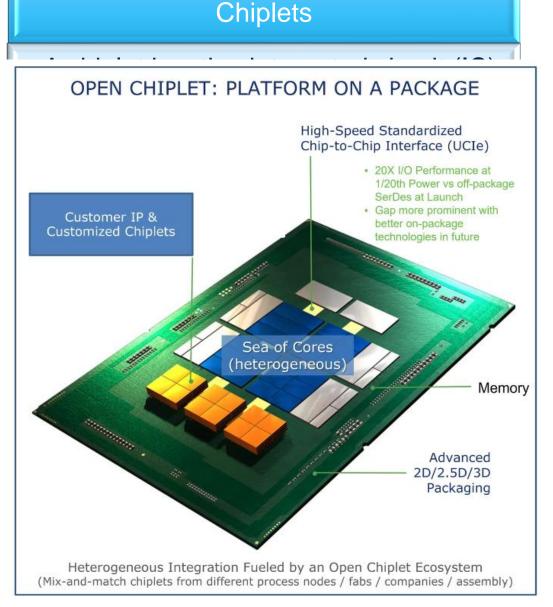

#### SIP, Chiplets

#### SIP

SiP: System in a package are like systems on a chip (SoCs) but less tightly integrated and not on a single semiconductor die. SiP solutions may require multiple packaging technologies, such as flip chip, wire bonding, wafer-level packaging and more

life.auamente

#### Multi die

#### • 3D IC packages save

- Save Area: Stacking components vertically, reducing surface area and bumping

- Increase performance: by shortening the space between chips.

- Reduce risks: in comparison to big die implementation

- Low costs: retaining high bandwidth and low power performance.

## 2D, 2.5D, 3D Packaging Options

| Organic Subs<br>Data Rate: >112<br>Line Space: >1<br>DRAM Die 1<br>Substrate<br>BGA Ball<br>2D | 2Gbps<br>0μm<br>Die 2      | RDL Fan<br>Data Rate: ><br>Line Space:<br>DRAM Dia<br>Substr<br>BGA F | 56Gbps<br>>2μm<br>ate                  | Data Rat<br>Line Spa<br>HBM<br>Inter | Interposer<br>e: 8~16Gbps<br>ace: >0.4µm<br>Die 1. Die 2.<br>Doser Die<br>ostrate<br>A Balls | Data                                                                       | orid Bonding<br>Rate: 4~6Gbps<br>Z PIQ<br>Die 1<br>Die 1<br>Substrate<br>GA Balls<br>3D |

|------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------|----------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Standard                                                                                       | <b>Data Rate</b><br>[Gbps] | <b>Bump Space</b><br>[um]                                             | <b>Power</b><br>Efficiency<br>[pJ/bit] | <b>Edge Density</b><br>[Tbps/mm]     | <b>Area Density</b><br>[Tbps/mm2]                                                            | <b>FOM-1</b><br>[Tbps/mm /<br>pJ/bit]<br><i>Larger is</i><br><i>better</i> | <b>FOM-2</b><br>[pJ/bit / mm]<br><i>Smaller is</i><br><i>better</i>                     |

| AIB 2.0                                                                                        | 6.4                        | 55                                                                    | 0.5                                    | 1.64                                 | -                                                                                            | 3.28                                                                       | 0.1                                                                                     |

| OpenHBI 1.0                                                                                    | 8                          | 40                                                                    | 0.4                                    | 2.29                                 | 2.04                                                                                         | 5.71                                                                       | 0.1                                                                                     |

| OpenHBI 2.0                                                                                    | 12~16                      | 40                                                                    | 0.5                                    | 3.34                                 | 3.06                                                                                         | 6.86                                                                       | 0.06                                                                                    |

| BoW - Basic                                                                                    | 8                          | 40                                                                    | 0.5                                    | 1.78                                 | 1.07                                                                                         | 3.56                                                                       | 0.1                                                                                     |

Parallel die-to-die interface standards for advanced packaging

Image courtesy: Synopsys, OCP Tech Week, Nov 2020)

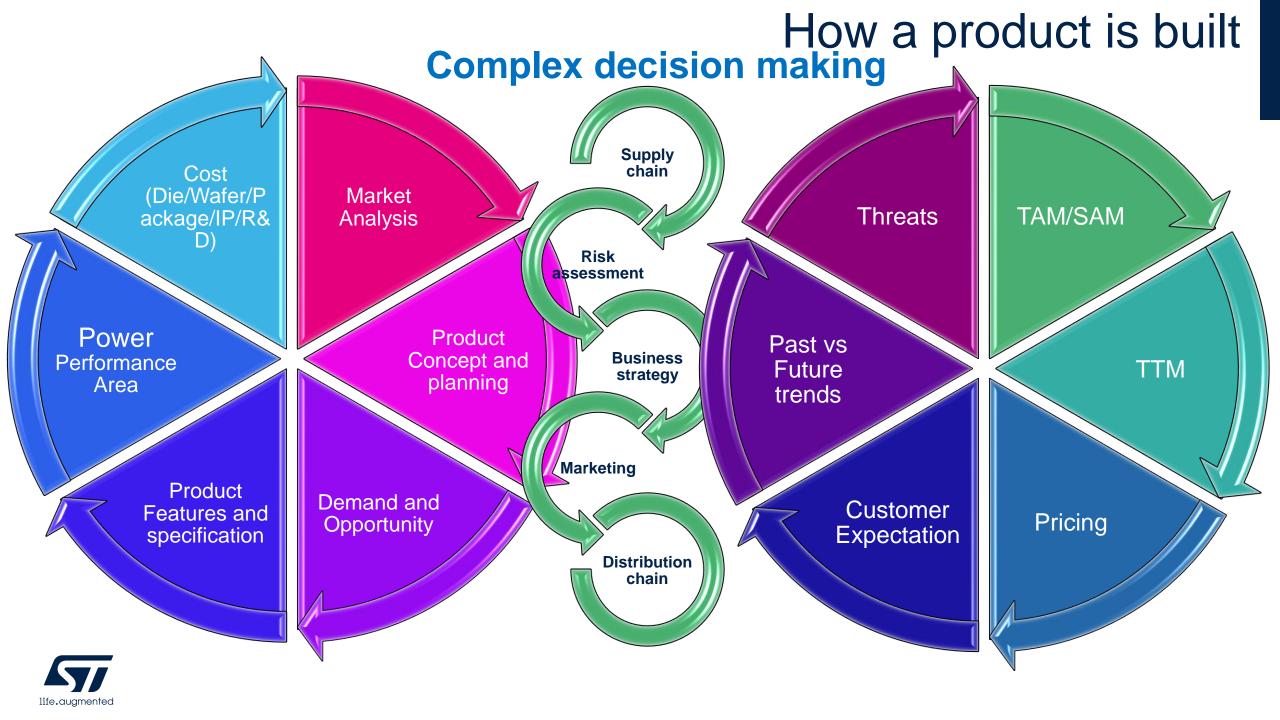

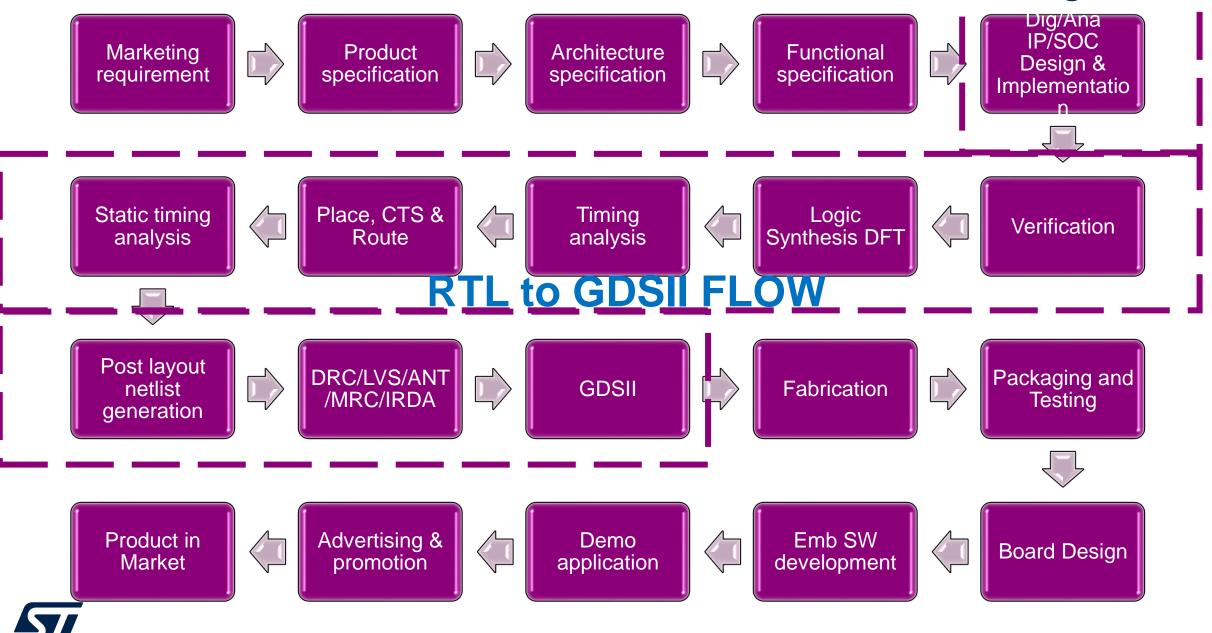

#### Let's see product design flow

#### Product design flow

life.augmented

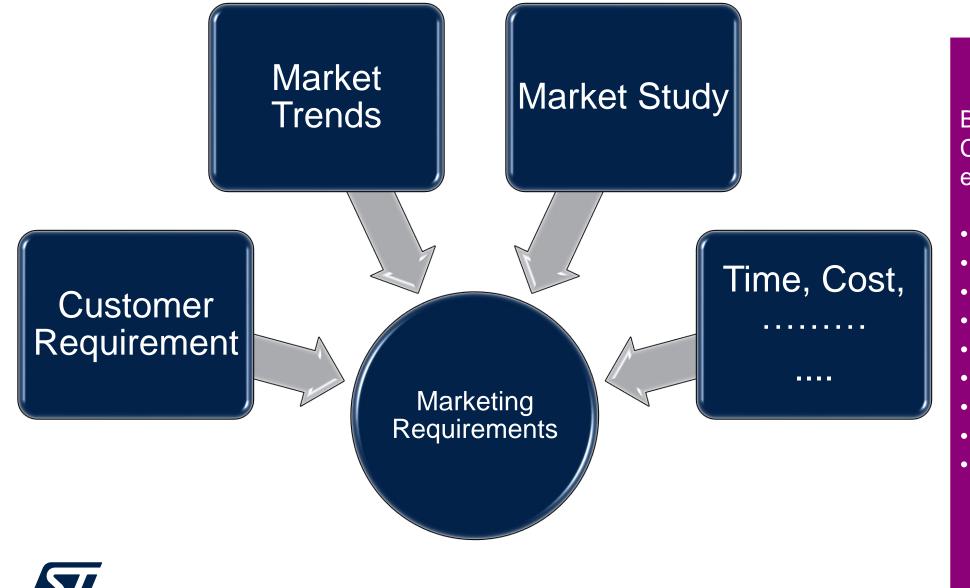

## Marketing

Brings to table Customer/Market expectations:

- Product name •

- **Business** case •

- Target market •

- Features superset

- Variants proposal •

- Road Map •

- Technology •

- SWOT •

. . .

#### Product Specification - Superset of requirements

Required Embedded Memory, Required performance, Required power management, Required connectivity

| Target<br>Processor<br>As per                                   | Memory Type and Size                | External Memory Requirements                                  |  |  |

|-----------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------|--|--|

| Security<br>Features                                            | System Memory requirements and Size | Video/Audio/Graphics<br>Features Requirement                  |  |  |

| Debug support<br>required                                       | Analog features<br>requirement      | No of IOs required                                            |  |  |

| and its associated<br>requirements<br>Specific<br>Requirement – | Digital Features<br>requirement     | External Connectivity requirements – USB, Ethernet, I2C, I3C, |  |  |

| MUST HAVE                                                       |                                     | GOOD to have features                                         |  |  |

life.auament

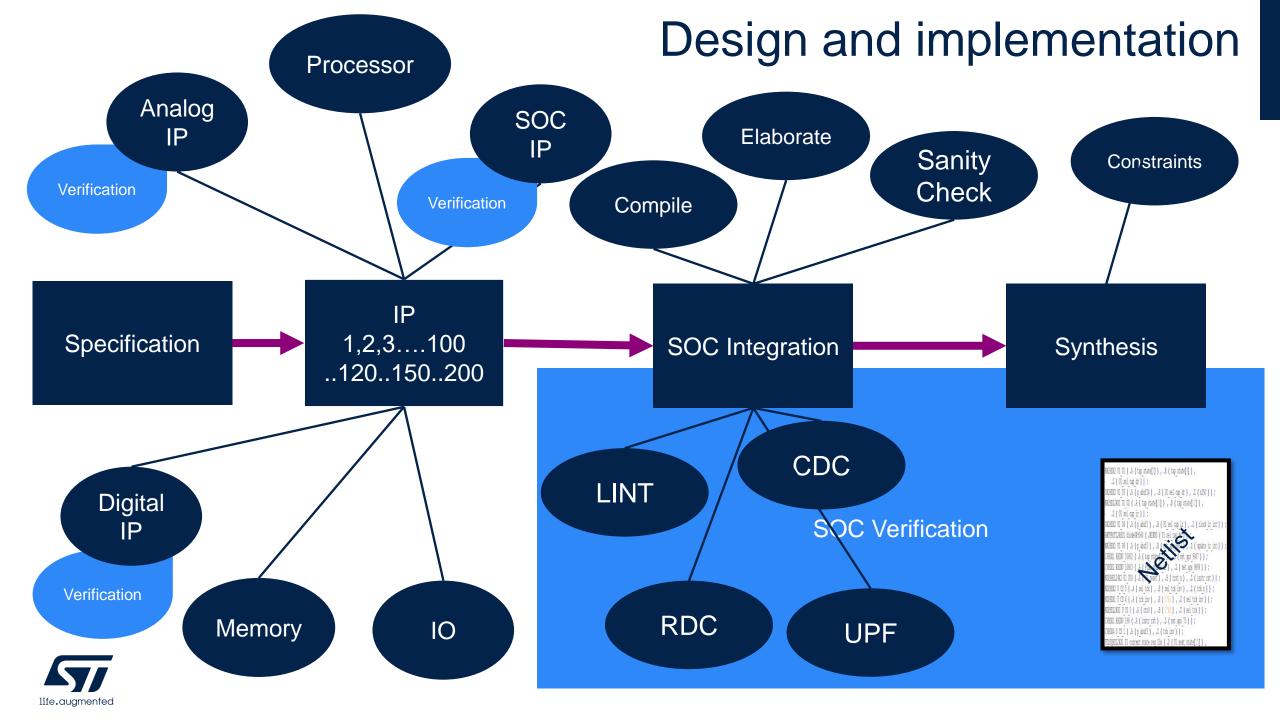

# Architecture – translating market expectation to specification

life.auamente

- Architecture specification

- IP(s) required, no of instances of IP, configuration of each IP

- Generic IP or SoC IP decision is taken

- Memory Map

- Interrupt Map

- DMA requirements

- Memory cuts requirements

- Frequency requirements

- Security Requirements

## **Datasheet**

#### STM32G473xB STM32G473xC STM32G473xE

Arm<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit MCU+FPU, up to 512 KB Flash, 170 MHz / 213 DMIPS, 128 KB SRAM, rich analog, math accelerator

- Core: Arm® 32-bit Cortex®-M4 CPU with FPU, Adaptive real-time accelerator (ART Accelerator) allowing 0-wait-state execution from Flash memory, frequency up to 170 MHz with 213 DMIPS, MPU, DSP instructions

- 7 x 12-bit DAC channels

- 16-channel DMA controller

life.augmented

- 5 x 12-bit ADCs 0.25 µs, up to 42 channels. Resolution up to 16-bit with hardware oversampling, 0 to 3.6 V conversion range

- 7 x ultra-fast rail-to-rail analog comparators

- 6 x operational amplifiers that can be used in PGA mode

- 14 timers

- Calendar RTC with alarm, periodic wakeup from stop/standby

- 3 x FDCAN, 4 x I2C , 5 x USART/UARTs, 1 x LPUART, 4 x SPIs, 1 x SAI, USB 2.0, USB Type-C, IRTIM

#### Chip/SOC Lead/Management

- A product is design under collaborative effort of various teams, people and individuals.

- Role of Chip Lead or SOC Lead or Project Lead is to act as bridge between various stakeholders.

## CDC/Lint/RDC

| Metastability                                                                                                                                                               | Reconvergence                                                                                                                                                          | Data                                                                | a hold (data<br>loss)                                                                                                                            | Design inte<br>across cloo<br>domains                                                                                                                                                      | ck                           | Reset<br>Synchronization                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>How do you<br/>ensure that you<br/>have handled<br/>metastability<br/>across clock<br/>domains, so it<br/>does not affect<br/>design<br/>functionality?</li> </ul> | <ul> <li>How do you<br/>ensure that a<br/>group of<br/>converging<br/>synchronized<br/>control signals<br/>are in sync at a<br/>particular clock<br/>cycle?</li> </ul> | ensu<br>from<br>dom<br>long<br>be c<br>the c<br>dom<br>slow<br>enat | do you<br>are that data<br>one clock<br>ain is held<br>enough to<br>aptured by<br>other clock<br>ain? (Fast to<br>clock, data<br>ole<br>uencing) | <ul> <li>How do you<br/>ensure that is<br/>sophisticated<br/>synchronization</li> <li>schemes (su<br/>as handshake<br/>FIFO) behave<br/>according to<br/>your<br/>specification</li> </ul> | d<br>ion<br>ich<br>ke,<br>'e | <ul> <li>How do you<br/>ensure that an<br/>asynchronous<br/>set/reset is<br/>properly<br/>synchronized for<br/>a set of flops and<br/>the reset is<br/>asynchronously<br/>asserted and<br/>synchronously<br/>de-asserted</li> </ul> |

| Different flows available for SoC CDC analysis.                                                                                                                             |                                                                                                                                                                        |                                                                     | Criteria                                                                                                                                         | Full Chip in normal flow                                                                                                                                                                   | IP_BLOC                      | CK Full chip with<br>abstraction flow                                                                                                                                                                                               |

| Grey box (ip_block) approach.                                                                                                                                               |                                                                                                                                                                        |                                                                     | Synthesis required for<br>blocks ?                                                                                                               | Yes                                                                                                                                                                                        | Yes                          | No                                                                                                                                                                                                                                  |

|                                                                                                                                                                             |                                                                                                                                                                        |                                                                     | Run-time                                                                                                                                         | High                                                                                                                                                                                       | Mediun                       | n Low                                                                                                                                                                                                                               |

| Full flat approach.                                                                                                                                                         |                                                                                                                                                                        |                                                                     | Noise                                                                                                                                            | High                                                                                                                                                                                       | Mediun                       |                                                                                                                                                                                                                                     |

| Abstraction based approach.                                                                                                                                                 |                                                                                                                                                                        |                                                                     | IP validation checks                                                                                                                             | No                                                                                                                                                                                         | No                           | Yes                                                                                                                                                                                                                                 |

|                                                                                                                                                                             |                                                                                                                                                                        |                                                                     | Convergence checks<br>Functional checks                                                                                                          | Yes<br>Yes                                                                                                                                                                                 | No<br>Yes                    | Yes<br>No                                                                                                                                                                                                                           |

| There are pros and                                                                                                                                                          | SGDC complexity<br>/Setup Effort                                                                                                                                       | High                                                                | Mediun                                                                                                                                           |                                                                                                                                                                                            |                              |                                                                                                                                                                                                                                     |

|                                                                                                                                                                             |                                                                                                                                                                        |                                                                     | SDC complexity                                                                                                                                   | High                                                                                                                                                                                       | Mediun                       | n Low                                                                                                                                                                                                                               |

## Low Power

| Combinational<br>Power Power | IO Power                                                                                                                                                                                                                                              | Memory<br>Power                                                                                                                                                                              | Clock Po                                                                                                                                                                                                         | ower                                                                                                                          |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| What can be done ?           | Leakage Internal Switching                                                                                                                                                                                                                            | Leakage           Sequential         2.368           Clock_cell         0.188           Memory         5.53           Combinational         28.7336           IO         45.35           PLL | Switching         Internal           40.475         160.38           26.52         24.531           19.38         177.28           490.38         350.86           0.155         0           SAMP         576.91 | Total           203.223           51.239           202.19           869.9736           45.505           16           1388.131 |  |

| Architecture Level           | <ul><li>Module level clock ga</li><li>Voltage scaling</li></ul>                                                                                                                                                                                       | ating. Frequ                                                                                                                                                                                 | ency scaling                                                                                                                                                                                                     |                                                                                                                               |  |

| Implementation Level         | <ul><li>Automatic clock gating. Multi-vt design</li><li>Data pipelining</li></ul>                                                                                                                                                                     |                                                                                                                                                                                              |                                                                                                                                                                                                                  |                                                                                                                               |  |

| RTL Level                    | <ul> <li>Clock gating, managing clock enable in data. Shift registers, grey pointers, state machine optimization., IDLE bus management</li> <li>Memory optimization: slicing, throughput, SP vs DP</li> <li>Split big counters. Out of BOX</li> </ul> |                                                                                                                                                                                              |                                                                                                                                                                                                                  |                                                                                                                               |  |

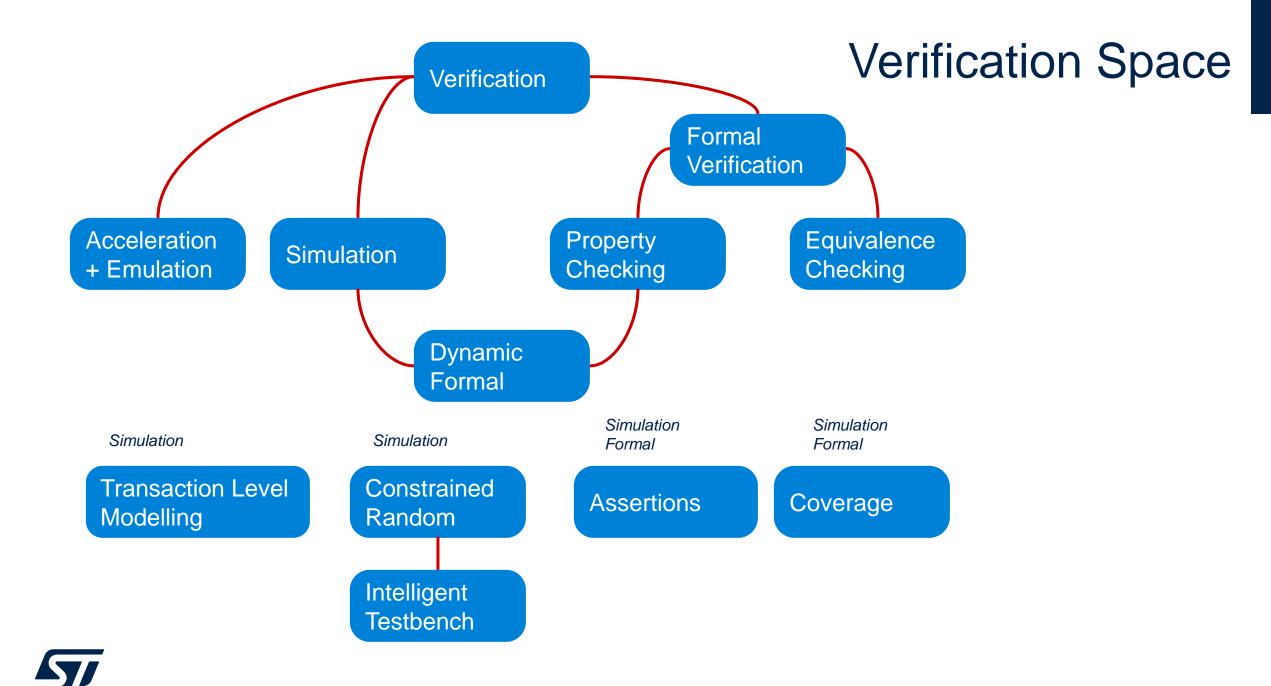

## Verification

## **SoC Verification**

- Connectivity

- Interoperability

- Performance Application Scenarios

Sub System Verification

- Connectivity

- Interoperability

- Performance -Application Scenarios

## **IP Verification**

- Functionality

- Protocol Compliance

- Standard Compliance

- Performance Application Scenarios

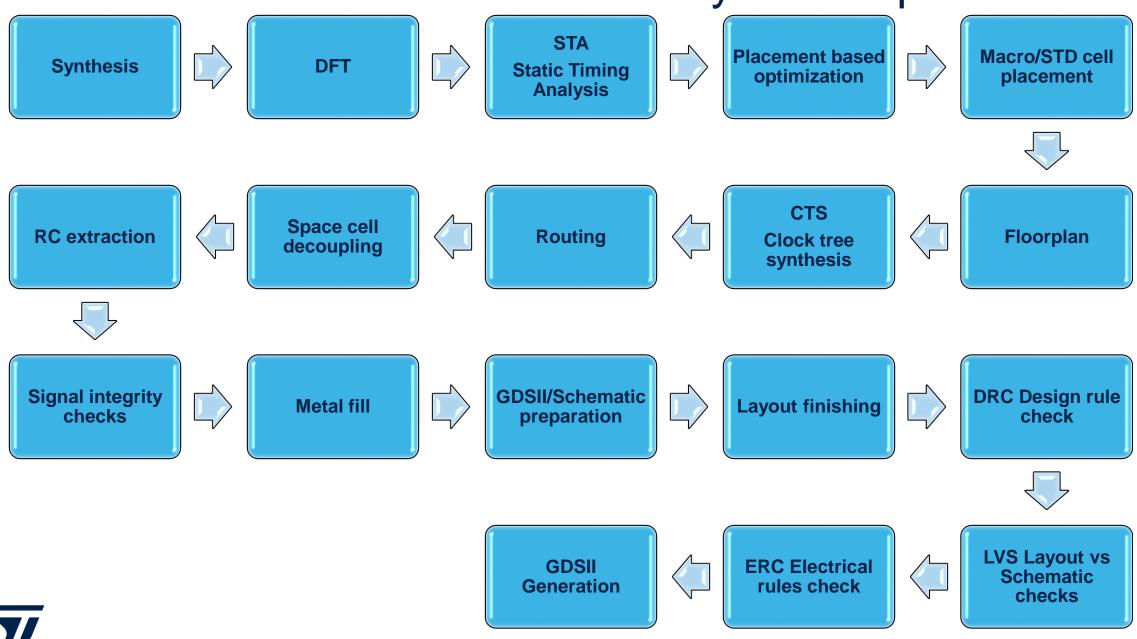

## **Physical Implementation**

## • A manufacturing step that ensures that the physical device, manufactured from the synthesized design, has no manufacturing defect.

| Architecture and Specification   | DFT Architecture under discussion                                                                                                                                                                               |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTL design and synthesis         | SCAN ports definition at IP/SoC level. DFT IP design                                                                                                                                                            |

| Logic synthesis and optimization | <ul><li>Synthesis optimization may affect testability</li><li>DFT under consideration</li></ul>                                                                                                                 |

| Floor planning and Placement     | <ul> <li>DFT considerations start to become critical</li> <li>Specific areas for test logic, scan chains and test access mechanism are allocated within the chip</li> </ul>                                     |

| Clock tree synthesis (CTS)       | <ul> <li>CTS can impact DFT, particularly in ensuring scan chains have<br/>balanced clock latencies for proper testing</li> </ul>                                                                               |

| Routing                          | <ul> <li>Testability considerations, such as avoiding routing congestions<br/>around DFT structures are investigated</li> </ul>                                                                                 |

| DFT Insertion                    | <ul> <li>DFT structures are added to the design to enable efficient testing.<br/>Scan chain insertion, Boundary Scan, Built in self test and test<br/>compression</li> </ul>                                    |

| Verification and Test generation | <ul> <li>After DFT structures insertion design is verified to ensure that TP<br/>can reaching and testing each FF or Memory element. ATPG tools<br/>create the test patterns for manufacturing tests</li> </ul> |

| Tape out                         | <ul> <li>After DFT insertion verification and generating TP, design is ready<br/>for TO</li> </ul>                                                                                                              |

## CAD and Methodology

#### • Infra management

- Project disk space, Version control system

- License EDA tools, EDA AE enablement

- NDA (Non-Disclosure Agreement)

- Co-ordination with IT team

- Flow & Methodology development

- Define methodology (process) to define common agreed way of working

- Flow development around EDA tool

- Custom Flow development (in-house scripts)

- Automation to convert external vendor provided data structure as per STM needs

- Local support to design team on STM internal tools, created by global teams

- Productivity: Avoid effort on tasks which are repetitive in nature

- Re-use: Maximum re-use as created flows are generic & scalable

- Quality: Same issue doesn't get repeated once fixed

- Design: Allow design team to focus on actual design issues

- Business: Allow to meet 'time to market' due to zero effort on repeated tasks

## EDA Tools in RTL2GDS flow

|                                                | Tool Name                                                                                                                                                       |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Documentation                                  | IPXACT                                                                                                                                                          |

| Modelling                                      | SVRN - System Verilog Real Numbers, C/C++, MATLAB, SciLAB, UML                                                                                                  |

| Scripting                                      | Python, Shell, PERL                                                                                                                                             |

| High Level Synthesis                           | Catapult, HDL Coder, Vivado                                                                                                                                     |

| RTL Design                                     | VHDL, Verilog, System Verilog                                                                                                                                   |

| Verification Language, Methodology, Simulators | Language (Verilog, System Verilog, C, Assembly)<br>Methodology (UVM, Metric Driven)<br>Formal Tools (CDNS JG Apps, VCS)<br>Simulators (Xcelium, VCS, QuestaSim) |

| Emulation/Acceleration                         | Veloce, Zebu, Palladium, Protium                                                                                                                                |

| Coverage Analysis                              | Siemens Questa Cover, CDNS Incisive Enterprise Simulator (IES), SNPS VC Formal                                                                                  |

| Synthesis                                      | SNPS DC, CDNS Genus, Siemens Précision                                                                                                                          |

| Floor planning, Placement, Routing, CTS        | CDNS Innovas, SNPS ICC2, Siemens Olympus-SOC, Siemens Calibre                                                                                                   |

| DRC/LVS                                        | CDNS Virtuoso, SNPS IC Validator, Siemens Calibre                                                                                                               |

| Static Timing Analysis                         | SNPS PrimeTime, CDNS Tempus, Siemens Calibre                                                                                                                    |

| Power Analysis                                 | SNPS Primepower. CDNS Tempus, Siemens Calibre                                                                                                                   |

| Scan Insertion                                 | SNPS DFT Compiler, CDNS Encounter Test, and Siemens Tessent                                                                                                     |

| ATPG                                           | SNPS TetraMAX, CDNS Encounter Test, Siemens Tessent                                                                                                             |

| Boundary Scan                                  | Corelis ScanExpress, JTAG Technologies ProVision, and XJTAG                                                                                                     |

| Memory BIST                                    | Synopsys STAR Memory System, Cadence Encounter Test, and Mentor Graphics Tessent                                                                                |

| Logic BIST                                     | Synopsys TetraMAX DFTMAX, Cadence Encounter Test, and Mentor Graphics Tessent                                                                                   |

| DFT Compilers                                  | Synopsys DFTMAX, Cadence Encounter Test, and Mentor Graphics Tessent.                                                                                           |

| Fault Simulation                               | SNPS VCS Fault, CDNS Incisive Enterprise Simulator                                                                                                              |

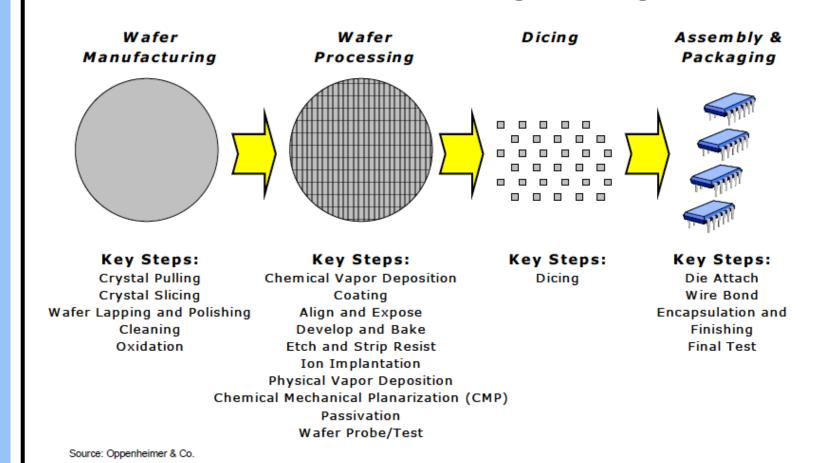

- Semiconductor devices are manufactured in Wafer fabs through a process known known as wafer fabrication.

- Circular wafers of silicon are put through a cycle of chemical processes in order to etch an ioncharged transistor array as patterned on a set of masks.

- On top of the transistor array, layers of metal interconnect form pathways between the transistors; the layers are insulated by a dielectric material

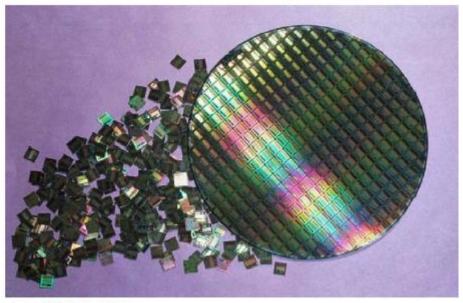

- After wafer processing, the finished wafer is put through a dicing process, where individual die are separated.

- These are sent to a back-end facility for packaging and assembly and final test.

life.auamented

## Fabrication

#### • Semiconductor Manufacturing flow

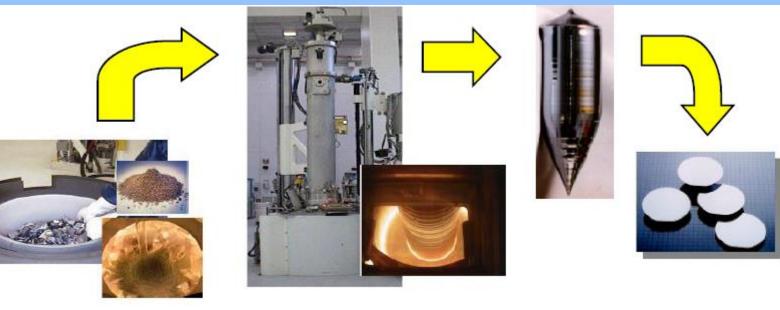

## Wafer Manufacturing

- Silicon wafers are produced by heating a mixture of silica and carbon in a furnace, creating wafer-grade silicon.

- A seed is then dipped into the molten silicon and is slowly twisted and pulled out.

- This creates a cylindrical ingot several feet long, which is ground to an appropriate diameter (200mm, 300mm, etc.).

- The ingot is then sliced into thin wafers for shipment to IDMs and foundries.

Source: MEMC, Oppenheimer & Co.

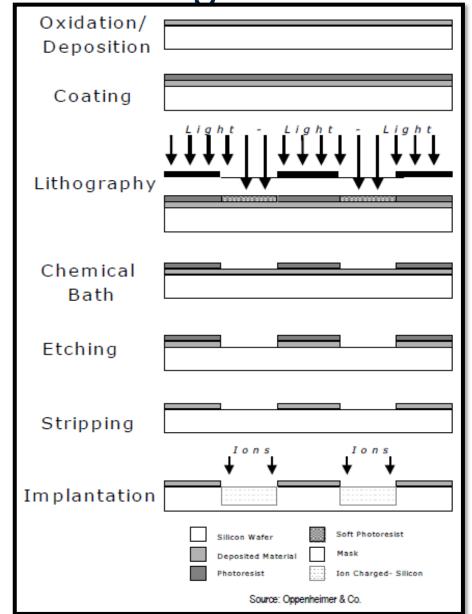

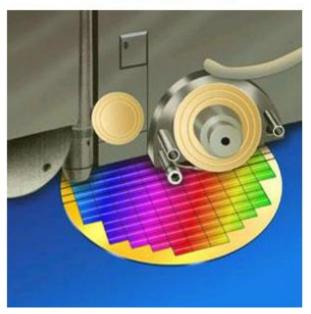

## Wafer Processing – Pre-Metal

- In the pre-metal stage, wafers are put through an intense cycle of chemical processes in order to etch a transistor array patterned on a set of masks.

- Through cycles of *deposition/oxidation, photolithography*, *etching*, and *ion implantation*, the transistor array is created.

- Charged ions are then deposited to enable transistor functionality.

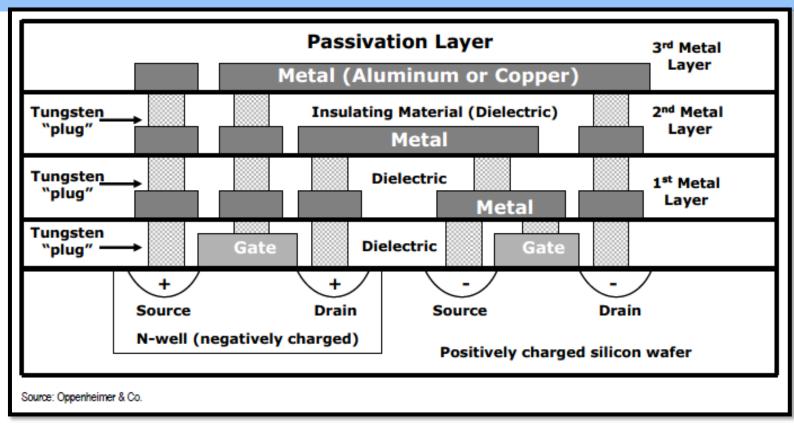

## Wafer Processing - Interconnect

- After the transistors are created, they are connected to form logic gates using an interconnect material, usually aluminum or copper.

- The metal layers are built with stages of deposition, lithography, and etching, similar to the premetal stage but using separate equipment and masks.

- Dielectric material is deposited between the layers to insulate them from one another.

- After the wafer is processed, a diamond drill is used to slice the wafer into individual die.

- Each die is tested before being sent to the back-end facility.

#### Semiconductor Dicing Diamond Drill

#### Finished Wafer and Individual Die

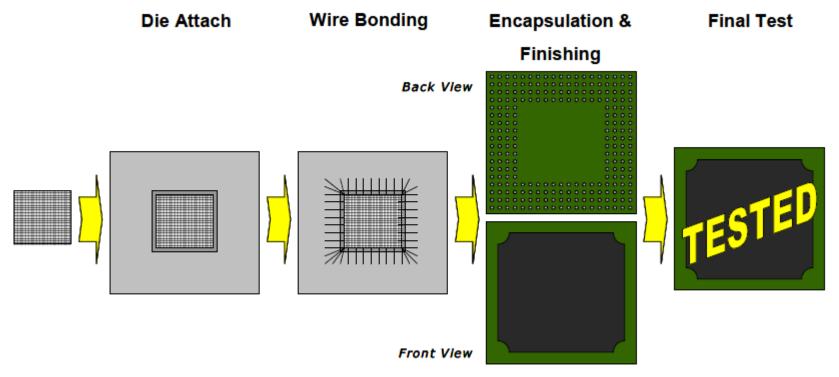

## Back End: Assembly and Test

• The individual die are sent to a back-end assembly facility, where they are attached to a package, wire bonded, encapsulated, and run through final test.

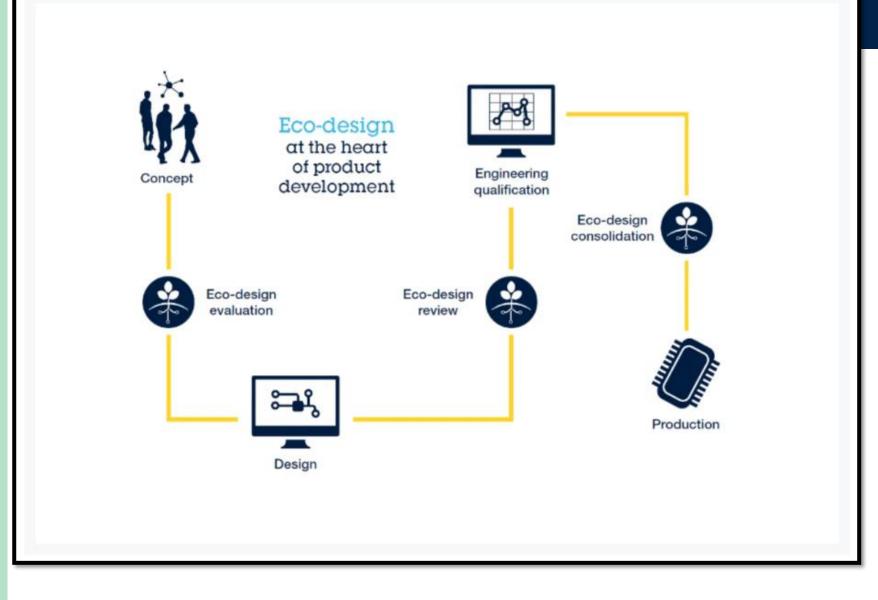

#### Environmentally & socially responsible products & applications

- We identify and promote innovative products that provide society with environmental and social benefits. In our Sustainable Technology program, we classify our products into four categories of responsible products:

- Low carbon products

- Thanks to optimized conception, these products reduce the footprint of our production equipment, utilities, and supply chain.

- Power efficient products

- State-of-the-art in reducing electricity consumption or power losses, these products reduce the footprint of the end-devices they are embedded in.

- Planet friendly applications

- Products that are key contributors to green applications, such as automotive powertrain electrification, solar panels, LED lighting.

- Human welfare applications

- Products that are powerful enablers for medical, health, safety, and security applications.

## Sustainable Development

# How to be part of semiconductor industry

#### Knowledge

- Device Physics, Quantum effects

- Linear Algebra, probability, entropy, stochastic process

- Basics of Electrical Systems

- Basics of material science

- Signals and Systems

- Computer architecture (Advanced), microprocessor and microcontroller

- Electronics (Digital, Analog))

- Communication Theory

- Algorithms

- Digital Signal Processing

- VLSI (Architecture, Design, Verification, Physical Design, DFT, Mixed Signal Design, Fabrication)

#### **Skills**

- Passion, analytical thinking

- Digital electronics

- Analog fundamentals

- CMOS

- C, C++, Assembly Language

- VHDL, Verilog, System Verilog

- UVM

- Schematic, Layout design

- Scripting: UNIX, Shell, Perl, Python

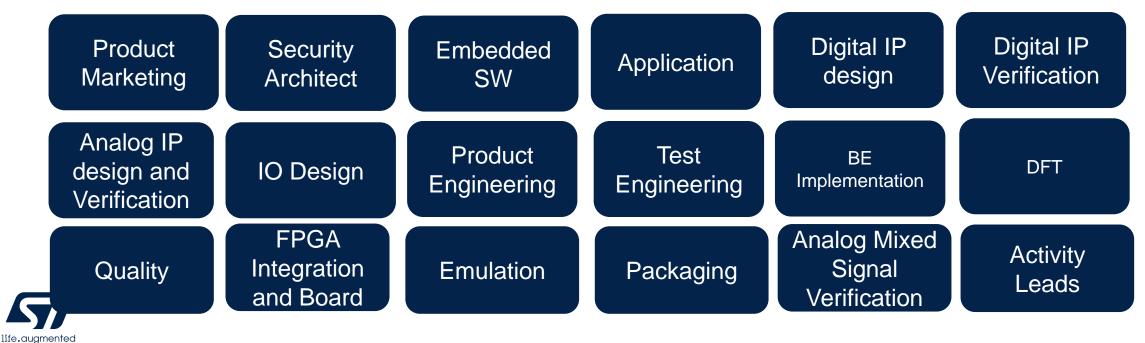

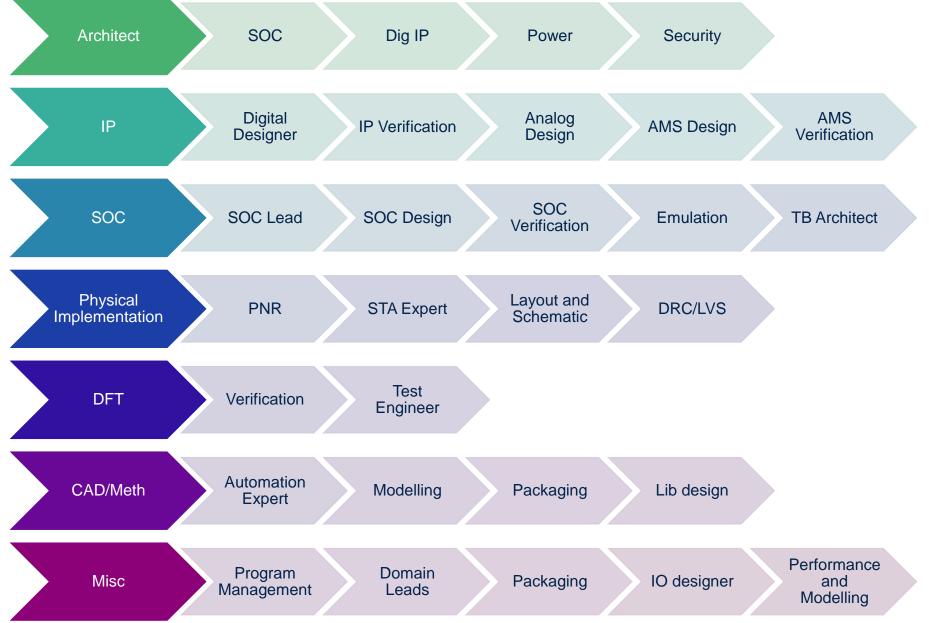

## Career Opportunities in VLSI domain

## Our technology starts with You

© STMicroelectronics - All rights reserved. ST logo is a trademark or a registered trademark of STMicroelectronics International NV or its affiliates in the EU and/or other countries. For additional information about ST trademarks, please refer to <u>www.st.com/trademarks</u>. All other product or service names are the property of their respective owners.

## **Back UP**

## Slides to add

- Research topics as part of sustainability slides

- 5 days flow from soc to industry

- UPF/Constraints

- Future applications

- Metric driven verification flow

- Skills/subjects required for VLSI

- Why VLSI as profession

- Importance of VLSI in our world semiconductors will decide geopolitics of world around us

- Speaker profile

- Addling laws of physics which play crucial role (slide 19)

## Validation

## Quality