# ARM<sup>®</sup> Versatile<sup>™</sup> Express Juno Development Platform

Revision: 1.0

V2M-Juno Technical Reference Manual

Confidential - Draft - Beta

## **Frontmatter**

## V2M-Juno Technical Reference Manual

Copyright © 2014 ARM. All rights reserved.

## Release information

## **Document History**

| Issue | Date Confidentiality |                      | Change                                          |  |

|-------|----------------------|----------------------|-------------------------------------------------|--|

| A-01  | 27 January 2014      | Confidential - Draft | First draft                                     |  |

| A-02  | 20 February 2014     | Confidential - Draft | Second draft                                    |  |

| A-03  | 17 March 2014        | Confidential - Draft | Beta release: Prototype board information added |  |

| A-03h | 08 May 2014          | Confidential - Draft | Draft for Alpha-3 CD                            |  |

## **Confidential Proprietary Notice**

This document is CONFIDENTIAL and any use by you is subject to the terms of the agreement between you and ARM or the terms of the agreement between you and the party authorised by ARM to disclose this document to you.

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information: (i) for the purposes of determining whether implementations infringe any third party patents; (ii) for developing technology or products which avoid any of ARM's intellectual property; or (iii) as a reference for modifying existing patents or patent applications or creating any continuation, continuation in part, or extension of existing patents or patent applications; or (iv) for generating data for publication or disclosure to third parties, which compares the performance or functionality of the ARM technology described in this document with any other products created by you or a third party, without obtaining ARM's prior written consent.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Frontmatter

Words and logos marked with ® or TM are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at <a href="http://www.arm.com/about/trademark-usage-guidelines.php">http://www.arm.com/about/trademark-usage-guidelines.php</a>

Copyright © [2014], ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20348

### **Confidentiality status**

This document is Confidential. This document may only be used and distributed in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

## **Product status**

The information in this document is for a Beta product, that is a product under development.

## Web address

http://www.arm.com

## Contents

# ARM® Versatile™ Express Juno Development Platform V2M-Juno Technical Reference Manual

|           | Pref  | ace                                                            |      |

|-----------|-------|----------------------------------------------------------------|------|

|           |       | About this book                                                | 7    |

|           |       | Feedback                                                       |      |

| Chapter 1 | Intro | oduction                                                       |      |

|           | 1.1   | Precautions                                                    | 1-12 |

|           | 1.2   | About the Versatile Express Juno Development Platform          | 1-13 |

|           | 1.3   | Location of components on the V2M-Juno motherboard             | 1-15 |

| Chapter 2 | Hard  | dware Description                                              |      |

|           | 2.1   | Overview of V2M-Juno motherboard hardware                      | 2-17 |

|           | 2.2   | Juno ARM Development Platform SoC                              | 2-21 |

|           | 2.3   | External power                                                 | 2-24 |

|           | 2.4   | Power control and Dynamic Voltage and Frequency Scaling (DVFS) | 2-25 |

|           | 2.5   | Clocks                                                         | 2-27 |

|           | 2.6   | Resets                                                         | 2-36 |

|           | 2.7   | Thin Links AXI master and slave interfaces                     | 2-39 |

|           | 2.8   | IOFPGA                                                         | 2-42 |

|           | 2.9   | HDLCD interface                                                | 2-45 |

|           | 2.10  | Interrupts                                                     | 2-47 |

|           | 2.11  | USB 2.0 interface                                              | 2-50 |

|           | 2.12  | SMC 10/100 Ethernet interface                                  | 2-51 |

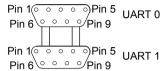

|              | 2.13                | UART interface                                               | 2-52       |  |  |  |

|--------------|---------------------|--------------------------------------------------------------|------------|--|--|--|

|              | 2.14                | Keyboard and mouse interface                                 | 2-53       |  |  |  |

|              | 2.15                | Additional user key entry                                    | 2-54       |  |  |  |

|              | 2.16                | Debug and trace                                              | 2-56       |  |  |  |

| Chapter 3    | Confi               | guration                                                     |            |  |  |  |

|              | 3.1                 | Overview of the V2M-Juno motherboard configuration system    |            |  |  |  |

|              | 3.2                 | Configuration process and operating modes                    | 3-63       |  |  |  |

|              | 3.3                 | Configuration files                                          | 3-68       |  |  |  |

|              | 3.4                 | Configuration switches                                       | 3-73       |  |  |  |

|              | 3.5                 | Use of reset push buttons                                    | 3-75       |  |  |  |

|              | 3.6                 | Command-line interface                                       | 3-76       |  |  |  |

| Chapter 4    | Progr               | rammers Model                                                |            |  |  |  |

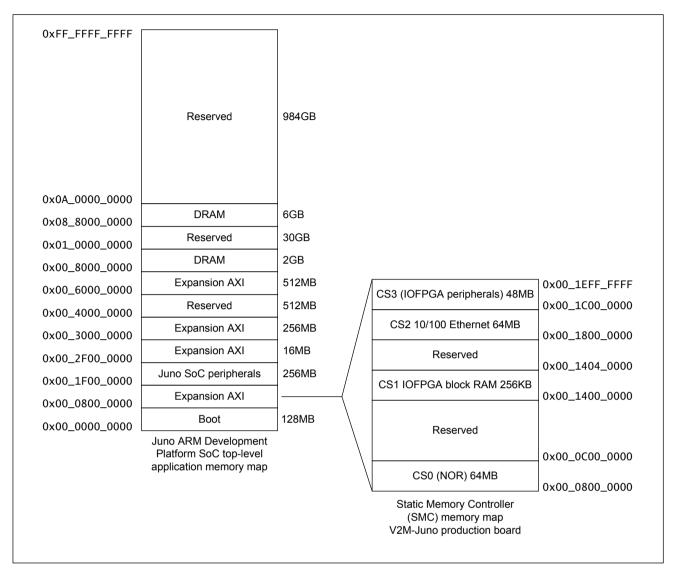

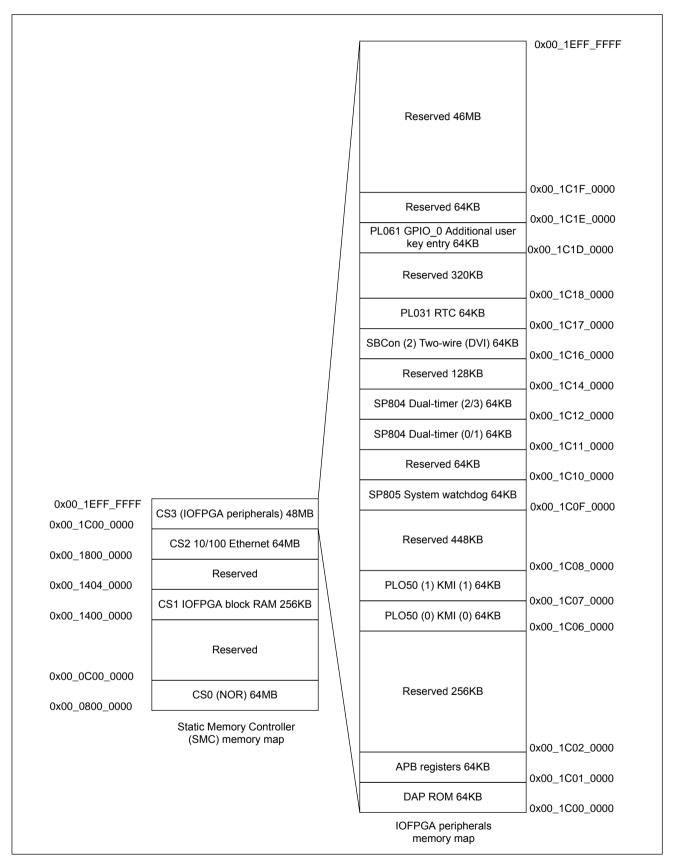

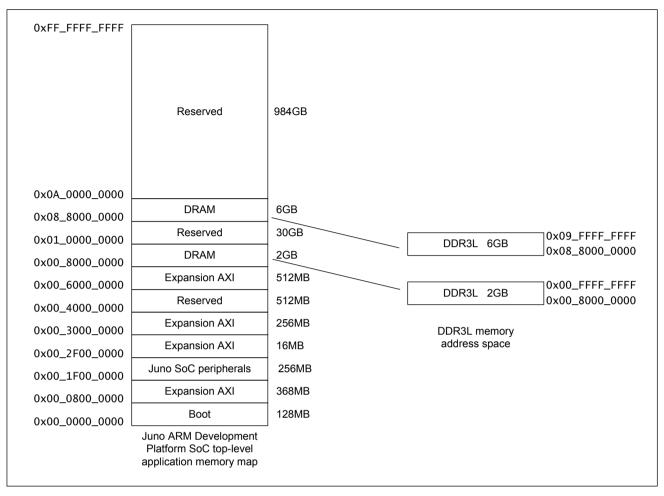

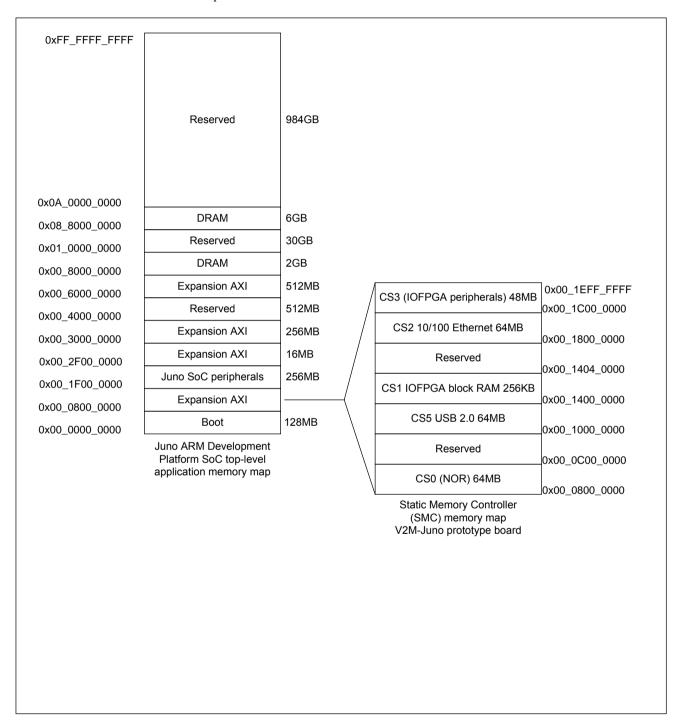

|              | 4.1                 | About this programmers model                                 | 4-80       |  |  |  |

|              | 4.2                 | V2M-Juno motherboard memory maps                             | 4-81       |  |  |  |

|              | 4.3                 | APB system registers                                         | 4-87       |  |  |  |

|              | 4.4                 | APB system configuration registers                           | 4-96       |  |  |  |

|              | 4.5                 | APB energy meter registers                                   | 4-100      |  |  |  |

| Appendix A.1 | Signal Descriptions |                                                              |            |  |  |  |

|              | A.1.1               | Debug connectors                                             | Appx-A-115 |  |  |  |

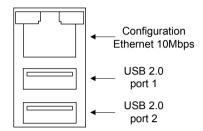

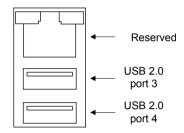

|              | A.1.2               | Configuration 10Mbps Ethernet and dual-USB connector         | Appx-A-119 |  |  |  |

|              | A.1.3               | Dual-USB connector                                           | Appx-A-120 |  |  |  |

|              | A.1.4               | SMC 10/100 Ethernet connector                                | Appx-A-121 |  |  |  |

|              | A.1.5               | Configuration USB connector                                  | Appx-A-122 |  |  |  |

|              | A.1.6               | Header connectors                                            | Appx-A-123 |  |  |  |

|              | A.1.7               | Keyboard and Mouse (KMI) connector                           | Appx-A-124 |  |  |  |

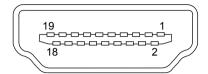

|              | A.1.8               | HDMI connectors                                              | Appx-A-125 |  |  |  |

|              | A.1.9               | Dual UART connector                                          | Appx-A-126 |  |  |  |

|              | A.1.10              | Secure keyboard and user push buttons connector              | Appx-A-128 |  |  |  |

|              | A.1.11              | ATX power connector                                          | Аррх-А-129 |  |  |  |

| Appendix B.2 | Proto               | type V2M-Juno motherboard                                    |            |  |  |  |

|              | B.2.1               | Overview of the prototype V2M-Juno motherboard               | Appx-B-131 |  |  |  |

|              | B.2.2               | Location of components on the prototype V2M-Juno motherboard | Appx-B-132 |  |  |  |

|              | B.2.3               | IOFPGA internal architecture with SMC USB ports              | Appx-B-133 |  |  |  |

|              | B.2.4               | SMC memory map of the prototype V2M-Juno motherboard         | Appx-B-135 |  |  |  |

|              | B.2.5               | SMC USB 2.0 connectors                                       | Аррх-В-137 |  |  |  |

| Appendix C.3 | Speci               | fications                                                    |            |  |  |  |

|              | C.3.1               | Electrical specification                                     | Аррх-С-139 |  |  |  |

| Appendix D.4 | Revis               | ions                                                         |            |  |  |  |

|              | D.4.1               | Revisions                                                    | Appx-D-141 |  |  |  |

## **Preface**

This preface introduces the  $ARM^{\circ}$   $Versatile^{*}$  Express Juno Development Platform V2M-Juno Technical Reference Manual.

It contains the following:

- About this book on page 7.

- Feedback on page 10.

## About this book

This book describes the Versatile Express Juno Development Platform (V2M-Juno)

## Product revision status

The rnpn identifier indicates the revision status of the product described in this book, where:

rn

Identifies the major revision of the product.

рn

Identifies the minor revision or modification status of the product.

## Intended audience

This book is written for experienced hardware and software developers to aid ARMv8 software and tooling development in the Juno ARM Development Platform SoC using the V2M-Juno motherboard.

## Using this book

This book is organized into the following chapters:

## **Chapter 1 Introduction**

This chapter provides an introduction to the Versatile Express Juno Development Platform.

## **Chapter 2 Hardware Description**

This chapter describes the Versatile Express V2M-Juno motherboard hardware.

## **Chapter 3 Configuration**

This chapter describes the powerup and configuration process of the Versatile Express V2M-Juno motherboard.

## Chapter 4 Programmers Model

This chapter describes the programmers model of the Versatile Express V2M-Juno motherboard.

## Appendix A.1 Signal Descriptions

This appendix describes the signals present at the interface connectors of the Versatile Express V2M-Juno motherboard.

## Appendix B.2 Prototype V2M-Juno motherboard

This appendix describes the Versatile Express V2M-Juno motherboard that provides two SMC USB 2.0 ports.

## Appendix C.3 Specifications

This appendix contains the electrical specifications of the Versatile Express V2M-Juno motherboard

## Appendix D.4 Revisions

This appendix describes the technical changes between released issues of this book.

## Glossary

The ARM Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See the *ARM Glossary* for more information.

## **Typographic conventions**

italic

Introduces special terminology, denotes cross-references, and citations.

## bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

## monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

## monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

## monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

## monospace bold

Denotes language keywords when used outside example code.

### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

```

MRC p15, 0 <Rd>, <CRn>, <CRm>, <Opcode_2>

```

## SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *ARM glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

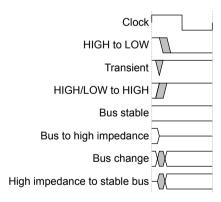

## **Timing diagrams**

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Figure 1 Key to timing diagram conventions

## **Signals**

The signal conventions are:

## Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals

- · LOW for active-LOW signals.

## Lower-case n

At the start or end of a signal name denotes an active-LOW signal.

## Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

## **ARM** publications

- Juno ARM® Development Platform SoC Technical Reference Manual (DDI 0515).

- Application Note AN415 Example LogicTile Express 20MG design for a V2M-Juno Motherboard (ARM DAI 0415).

- LogicTile Express™ 3MG Technical Reference Manual (DUI 0449).

- *ARM® LogicTile Express™ 13MG Technical Reference Manual* (ARM DUI 0556).

- LogicTile Express™ 20MG Technical Reference Manual (DDI 0498).

- ARM® CoreLink™ TLX-400 Network Interconnect Thin Links Supplement to ARM®

CoreLink™ NIC-400 Network Interconnect Technical Reference Manual (ARM DSU 0028).

- ARM® PrimeCell™ Technical Reference Manual Real Time Clock (PL031) (ARM DDI 0224).

- ARM PrimeCell PS2 Keyboard/Mouse Interface (PL050) (ARM DDI 0143).

- ARM PrimeCell™ General Purpose Input/Output (PLO61)Technical Reference Manual (ARM DUI 0142).

- ARM Dual-Timer Module (SP804) Technical Reference Manual (ARM DDI 0271).

- ARM Watchdog Module (SP805) Technical Reference Manual (ARM DDI 0270).

- CoreLink SMC-35x Static Memory Controller Series Technical Reference Manual (ARM DDI 0380).

- AMBA 3 AHB-Lite Protocol Specification v1.0 (ARM IHI 0033).

- AMBA 3 APB Protocol Specification v1.0 (ARM IHI 000024).

- *ARM DSTREAM® Setting up the Hardware* (ARM DUI 0481).

- ARM DSTREAM® and RVI® Using the Debug Hardware Configuration Utilities (ARM DUI 0498).

- CoreSight Components Technical Reference Manual (ARM DDI 0314).

## Other publications

See the Linaro website <a href="http://www.linaro.org/downloads/">http://www.linaro.org/downloads/</a> for Linaro software.

## **Feedback**

## Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

## Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title.

- The number ARM DDI0524A 03h.

- The page number(s) to which your comments refer.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

| Note —                                                                                                                                                    |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of represented document when used with any other PDF reader. | of the |

## Chapter 1 **Introduction**

This chapter provides an introduction to the Versatile Express Juno Development Platform. It contains the following sections:

- 1.1 Precautions on page 1-12.

- 1.2 About the Versatile Express Juno Development Platform on page 1-13.

- 1.3 Location of components on the V2M-Juno motherboard on page 1-15.

## 1.1 Precautions

This section contains advice about how to prevent damage to your V2M-Juno motherboard. This section contains the following subsections:

- 1.1.1 Ensuring safety on page 1-12.

- 1.1.2 Preventing damage on page 1-12.

## 1.1.1 Ensuring safety

An on-board connector supplies 12V DC to the Juno Development Platform.

——Warning ———

Do not use the Juno Development Platform near equipment that is sensistive to electromagnetic emissions, for example, medical equipment.

## 1.1.2 Preventing damage

The Juno Development Platform is intended for use within a laboratory or engineering development environment. It is supplied with an enclosure that leaves the board sensitive to electrostatic discharges and permits electromagnetic emissions.

——— Caution ————

To avoid damage to the Juno Development Platform, observe the following precautions:

- You must connect the external power supply to the board before powerup to prevent damage.

- Never subject the board to high electrostatic potentials. Observe Electrostatic Discharge (ESD) precautions when handling any board.

- · Always wear a grounding strap when handling the board.

- Only hold the board by the edges.

- Avoid touching the component pins or any other metallic element.

- Do not use the board near a transmitter of electromagnetic emissions.

## 1.2 About the Versatile Express Juno Development Platform

The Juno Development Platform, the V2M-Juno motherboard is a development motherboard that provides access to the Juno ARM Development Platform SoC. The Juno ARM Development Platform SoC is a development chip that supports ARMv8 software tooling, evaluation and development.

The V2M-Juno motherboard provides the following:

## Juno ARM Development Platform SoC (Juno SoC)

The Juno ARM Development Platform SoC provides a fully coherent dual-core Cortex-A57 cluster, a fully coherent quad-core Cortex-A53 cluster and an IO-coherent Mali-T624 quad-core GPU cluster.

The dual-core Cortex-A57 cluster contains a 2MB L2 cache and NEON and FPU operating at nominal 800MHz, overdrive 1.1GHz.

The quad-core A53 cluster has a 1MB L2 cache and NEON and FPU operating at nominal 700MHz, overdrive 850MHz.

The Mali-T624 quad-core cluster operates at nominal 600MHz, no overdrive.

Separate power domains support power management through *Dynamic Voltage and Frequency Scaling* (DVFS) of the A57, A53 and GPU clusters.

## LogicTile site

The V2M-Juno motherboard provides two headers that enable you to fit a Versatile Express LogicTile daughterboard. A Thin Links TLX Network Interconnect connects the motherboard and daughterboard.

## Powerup and configuration

An on-board EEPROM stores board and file identification information and a microSD card stores software images and configuration files. You can access the microSD card to perform configuration file editing and to update software images.

Configuration of the V2M-Juno motherboard and the LogicTile daughterboard, if fitted, proceeds automatically under the control of the *Motherboard Configuration Controller* (MCC) after powerup or reset.

You can customize the clock speeds and other configuration settings.

## **IOFPGA**

The IOFPGA provides low-bandwidth peripherals that the Juno SoC does not provide. The IOFPGA connects to the Juno SoC through a 32-bit *Static Memory Bus* (SMB) with dedicated chip selects.

The IOPFGA also contains energy meters, consisting of dedicated registers, that form part of the power control and DVFS system.

## External user memory

8GB on-board DDR3L 800MHz connects to memory interfaces in the Juno SoC. 64MB NOR Flash connects to the IOFPGA. The IOFPGA contains 256KB of user RAM.

## Access ports

The V2M-Juno motherboard provides access through a general-purpose dual-UART, SMC 10/100 Ethernet, four USB 2.0 ports, and keyboard and mouse ports.

Note

The prototype version of the V2M-Juno motherboard also provides two SMC USB 2.0 ports. See *B.2.1 Overview of the prototype V2M-Juno motherboard* on page Appx-B-131 for information.

## Video and audio output

The V2M-Juno motherboard provides dual HDMI outputs. The Juno SoC sends two independent 24-bit RGB video channels to the HDMI transmitters. Both HDMI ports share the same single I<sup>2</sup>S audio from the Juno SoC.

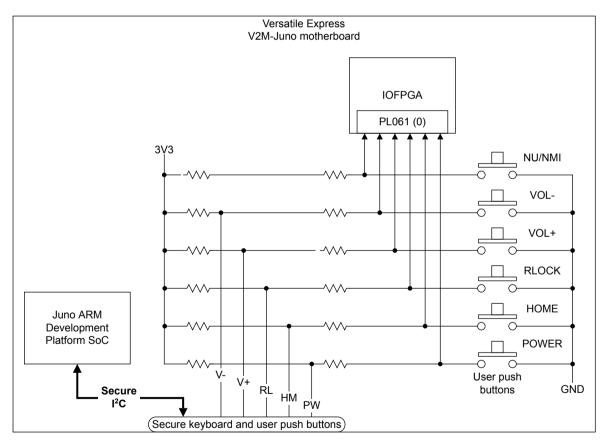

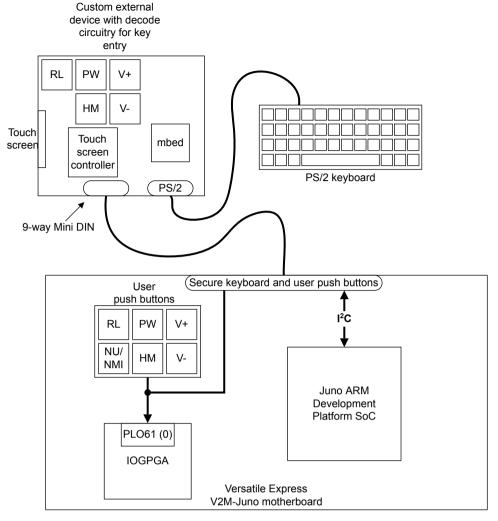

## Additional user key entry

The V2M-Juno motherboard supports trusted keyboard entry and additional key entry to simulate hand-held devices.

## **User LEDs**

The V2M-Juno motherboard provides eight user LEDs that connect to the IOFPGA. The meaning of these LEDs depend on the software that you implement in the Juno SoC.

## System LEDs

The V2M-Juno motherboard provides LEDs that denote the status of the board power supplies and read and write access to the configuration microSD card through the configuration USB port or configuration Ethernet port.

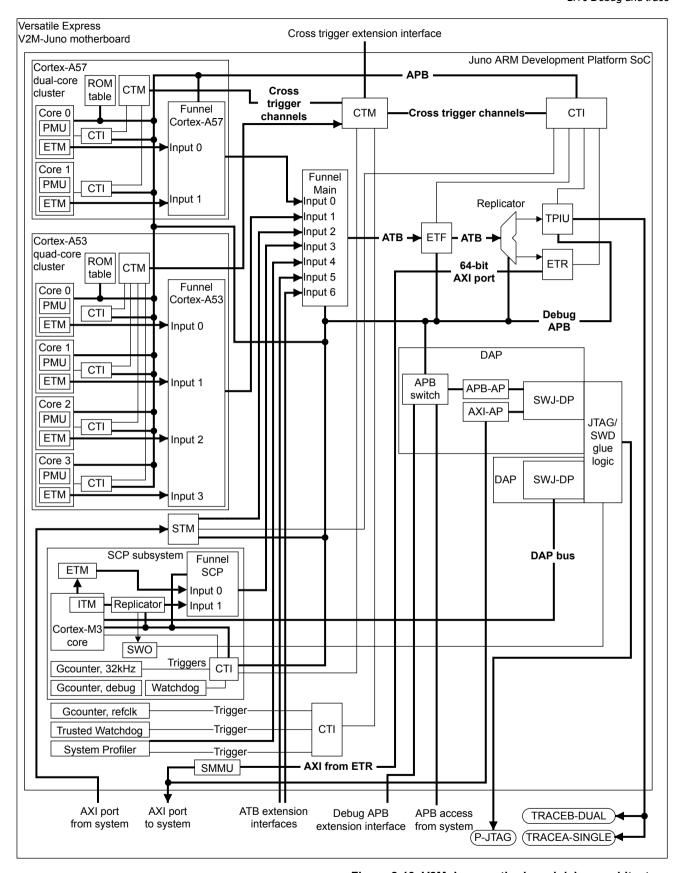

## Debug

The V2M-Juno motherboard supports P-JTAG Processor debug that enables connection of DSTREAM or a compatible third-party debugger. The board also supports 32-bit trace.

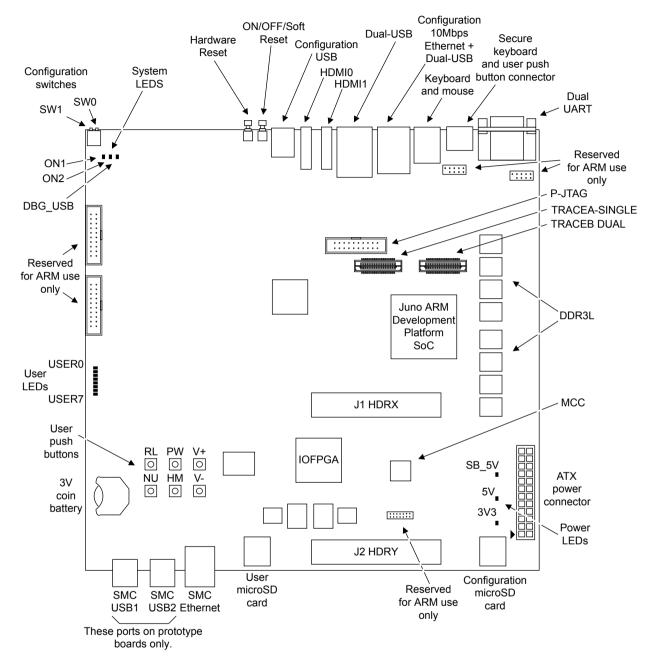

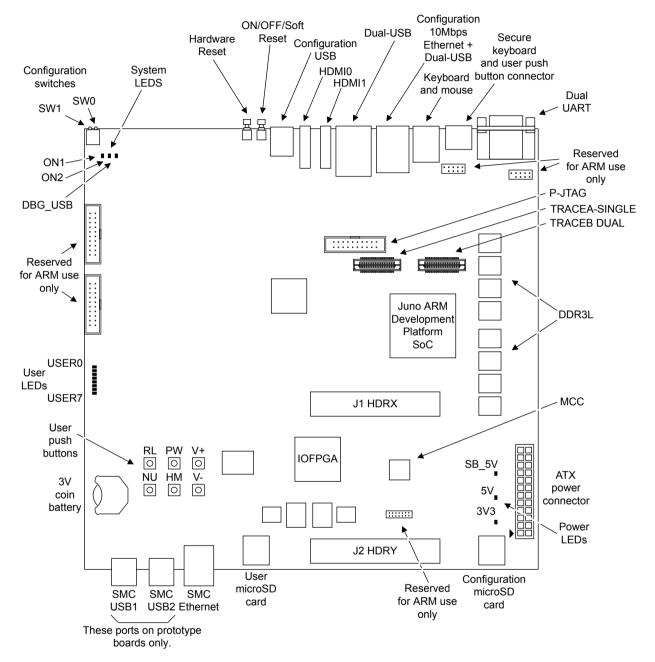

## 1.3 Location of components on the V2M-Juno motherboard

The following figure shows the physical layout of the upper face of the V2M-Juno motherboard.

Figure 1-1 V2M-Juno motherboard layout, upper face

| The production version of the V2M-Juno motherboard does not provide the SMC USB ports. The        |

|---------------------------------------------------------------------------------------------------|

| prototype V2M-Juno motherboard provides these ports. See B.2.1 Overview of the prototype V2M-Juno |

| motherboard on page Appx-B-131 for information on the prototype version of the V2M-Juno           |

| motherboard.                                                                                      |

Note

# Chapter 2 **Hardware Description**

This chapter describes the Versatile Express V2M-Juno motherboard hardware.

It contains the following sections:

- 2.1 Overview of V2M-Juno motherboard hardware on page 2-17.

- 2.2 Juno ARM Development Platform SoC on page 2-21.

- 2.3 External power on page 2-24.

- 2.4 Power control and Dynamic Voltage and Frequency Scaling (DVFS) on page 2-25.

- 2.5 Clocks on page 2-27.

- 2.6 Resets on page 2-36.

- 2.7 Thin Links AXI master and slave interfaces on page 2-39.

- 2.8 IOFPGA on page 2-42.

- 2.9 HDLCD interface on page 2-45.

- *2.10 Interrupts* on page 2-47.

- 2.11 USB 2.0 interface on page 2-50.

- 2.12 SMC 10/100 Ethernet interface on page 2-51.

- 2.13 UART interface on page 2-52.

- 2.14 Keyboard and mouse interface on page 2-53.

- 2.15 Additional user key entry on page 2-54.

- 2.16 Debug and trace on page 2-56.

2 Hardware Description 2.1 Overview of V2M-Juno motherboard hardware

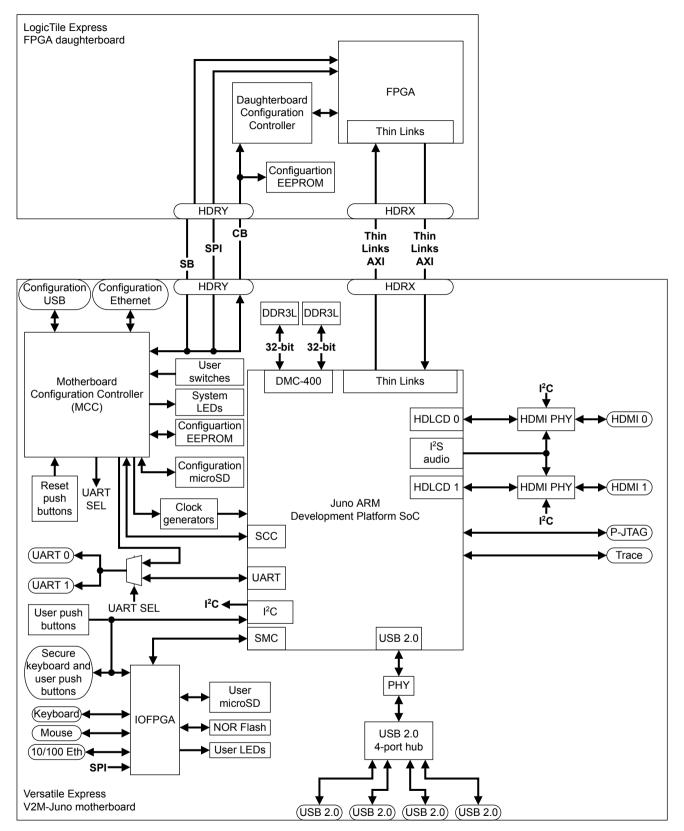

## 2.1 Overview of V2M-Juno motherboard hardware

The hardware infrastructure of the V2M-Juno motherboard supports ARMv8 software evaluation and tooling development using the Juno ARM Development Platform SoC.

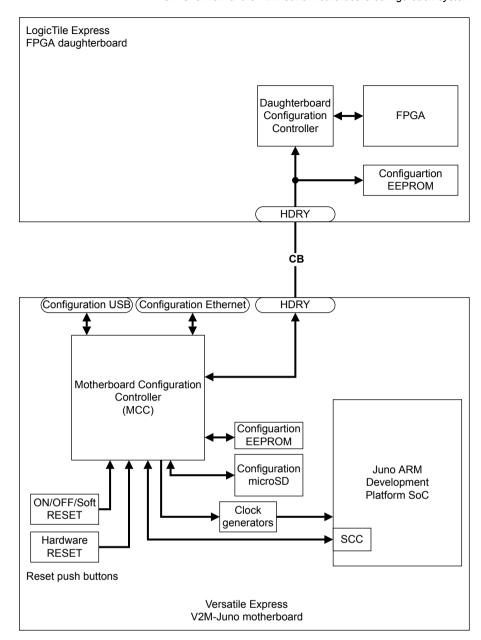

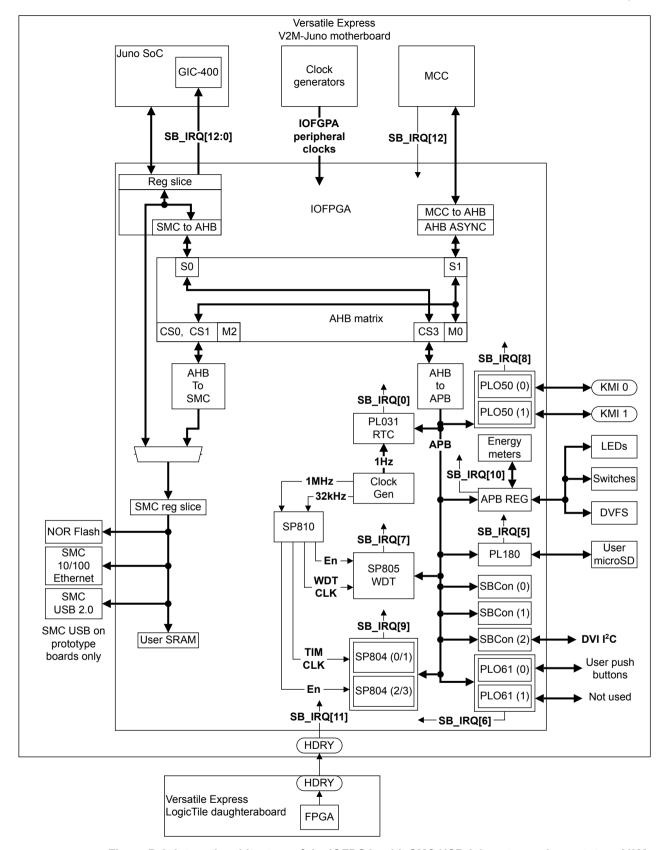

The following figure shows the hardware infrastructure of the V2M-Juno motherboard.

Figure 2-1 V2M-Juno motherboard system architecture with LogicTile FPGA daughterboard

The V2M-Juno motherboard contains the following components and interfaces:

• One Juno ARM Development Platform SoC:

2.1 Overview of V2M-Juno motherboard hardware

- Dual-core Cortex-A57, Quad-core Cortex-A53 and Mali-T624 quad-core GPU.

- Memory interfaces, HDLCD display controllers, and other on-chip peripherals.

- Site for LogicTile Express daughterboard:

- Two headers, *HDRX* and *HDRY*, enable you to fit any Versatile Express LogicTile daughterboard in this site.

- Thin Links AXI master and slave interfaces to LogicTile site.

- One ARM Cortex-M3 *Motherboard Configuration Controller* (MCC):

- Supports configuration of the Juno SoC and V2M-Juno motherboard at powerup or reset.

- Clock generator configuration.

- Loading of *Real Time Clock* (RTC) registers.

- Board configuration.

- Pre-loading of external memory.

- One microSD card that stores the following:

- Board configuration files.

- Software images.

- One EEPROM that stores board identification information and file names for the configuration system.

- Configuration ports.

The following ports support Drag-and-Drop editing of configuration files in the configuration microSD card:

- Configuration USB 2.0 port.

- Configuration 10Mbps Ethernet port.

- Two 32-bit 4GB DDR3L on-board memories:

- Low-power.

- 800MHz, 1600 million transfers per second (MTs).

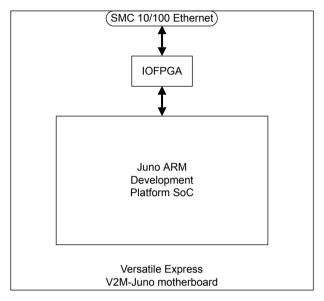

- Static Memory Controller (SMC) 10/100 Ethernet.

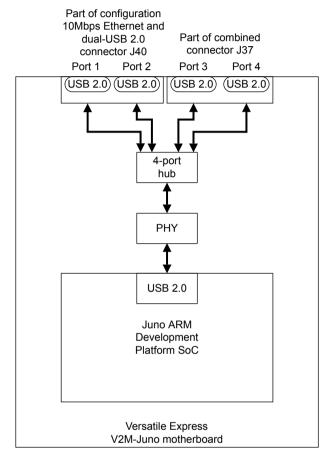

- Four USB 2.0 ports, USB 4-port hub and USB PHY.

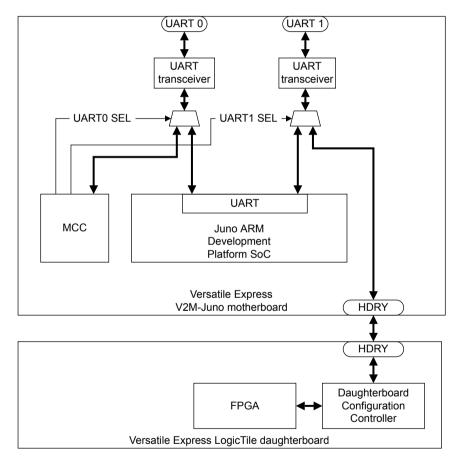

- Two UARTs:

- UART 0 can connect to the Juno SoC or to the MCC.

- UART 1 can connect to the Juno SoC or to the Daughterboard Configuration Controller on the LogicTile daughterboard fitted in the daughterboard site. The board configuration files, that you can edit using the configuration ports, determine the connectivity of the UART ports during runtime.

| Nota |  |  |

|------|--|--|

The Daughterboard Configuration Controller is a microcontroller on the LogicTile that controls the configuration of the daughterboard during powerup or reset.

- Two HDLCD ports that each support:

- HDMI 1.4a up to 1080p.

- One I<sup>2</sup>S four-channel stereo audio output.

- Four USB 2.0 ports, USB 4-port hub and USB PHY.

- Additional user key entry:

- Trusted User Keyboard entry using the secure keyboard connector.

- Additional user key entry using the push buttons on the V2M-Juno motherboard to simulate handheld devices.

- IOFPGA that contains registers that form part of the Power Control and DVFS system. The IOFPGA

also provides access to low-bandwidth peripherals, user switches and user LEDs that the Juno SoC

does not provide.

- 64MB NOR Flash.

- 256KB IOFPGA internal block RAM.

- User microSD card slot.

- Keyboard and Mouse ports.

- Six user push buttons for additional user key entry.

- System registers.

- Current, voltage, power and energy meters.

- Timers.

- Eight user LEDs. Application software defines their meaning.

| Note - |  |

|--------|--|

| Note   |  |

The prototype V2M-Juno motherboard also provides two SMC USB 2.0 ports that connect through the IOFPGA. See *B.2.1 Overview of the prototype V2M-Juno motherboard* on page Appx-B-131.

- · Nine programmable clock generators.

- A real-time clock in the MCC:

- A 3V coin battery powers the real-time clock when the board is powered down.

- Three system LEDs.

These LEDs connect to the MCC:

- ONI LED. Reserved for ARM use only.

- ON2 LED. Denotes ATX power supply powered up.

- *Debug USB* LED. Denotes read or write access to the configuration microSD card through the configuration USB 2.0 port.

- Debug ports:

- 32-bit CoreSight Trace port.

- Processor CoreSight debug (P-JTAG) port.

2 Hardware Description 2.2 Juno ARM Development Platform SoC

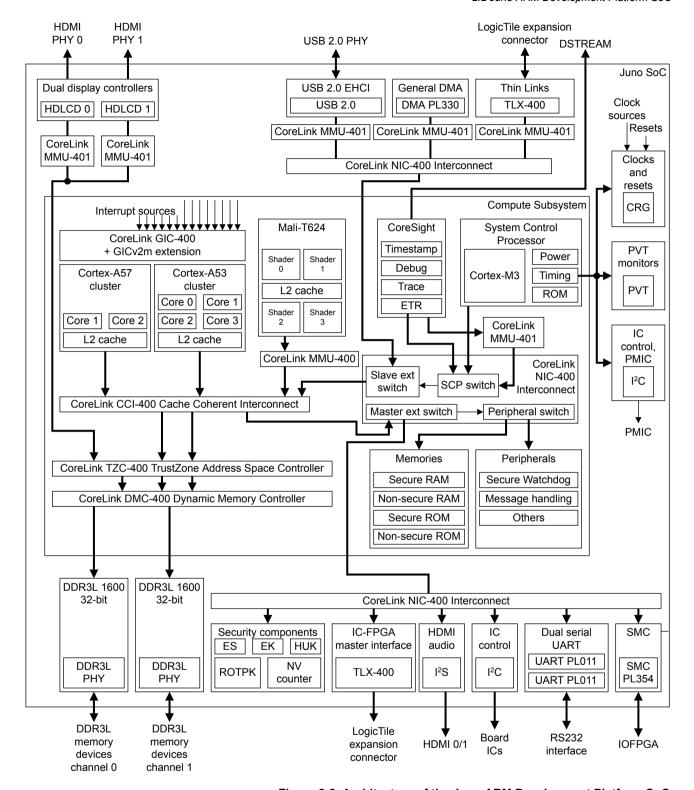

## 2.2 Juno ARM Development Platform SoC

This section provides an overview of the components of the Juno ARM Development Platform SoC. This development chip, or Juno SoC, provides a a dual-core Cortex-A57 cluster, quad-core Cortex-A53 cluster, a quad-core Mali-T624 graphics cluster, interfaces, on-chip peripherals and internal network connect.

The following figure shows the architecture of the Juno ARM Development Platform SoC.

Figure 2-2 Architecture of the Juno ARM Development Platform SoC

The Juno ARM Development Platform SoC contains the following components and interfaces.

- Dual-core Cortex-A57 cluster operating at nominal 800MHz, overdrive 1.1GHz:

- 2MB L2 cache.

- NEON and Floating Point Unit (FPU).

- Quad-core Cortex-A53 cluster operating at nominal 700MHz, overdrive 850MHz:

- 1MB L2 cache.

- NEON and *Floating Point Unit* (FPU).

- Mali-T624 quad-core GPU cluster operating at 600MHz.

- Internal AXI subsystem operating at up to 533MHz.

- Dual ARM HDLCD Display Controllers:

- Supports HDMI 1.4a up to 1080p.

- Dual DDR3L PHY and 32-bit DDR3L interfaces.

- Thin Links AXI master and slave interfaces to the LogicTile site. At the default clock frequency of 61.5MHz, the operating bit rates are:

- Master interface: 68Mbps in the forward direction and 78Mbps in the reverse direction.

- Slave interface: 246 Mbps in the forward direction and 305Mbps in the reverse direction.

| Note  |  |

|-------|--|

| 11016 |  |

The forward direction is from master to slave and the reverse direction is from slave to master.

- USB 2.0 Host Controller:

- 480Mbps ULPI interface to off-chip PHY.

- PL354 Static Memory Controller (SMC).

- PL330 Direct Memory Access (DMA) controller.

- CoreSight Processor debug (P-JTAG) and Trace.

- · APB subsystem:

- Dual-UART.

- I<sup>2</sup>S 4-channel stereo audio.

- Power, Voltage, and Temperature (PVT) monitoring of Juno ARM Development Platform SoC.

- Non-volatile counter. A real time clock that retains its stored value after powerdown.

- System Control Processor (SCP). This is a Cortex-M3 processor integrated into the Juno ARM Development Platform SoC. It initiates the system architecture and pre-load memory at powerup and performs power management and system control functions during runtime.

- I<sup>2</sup>C. This connects to HDMI controllers, the UART transceiver and other components on the V2M-Juno motherboard.

- Secure I<sup>2</sup>C. This connects to the Secure Keyboard.

- Keys. Encryption keys for signing software.

- Random-number generator. This operates with the encryption keys when validating software.

- System override registers that enable you to override various aspects of the Juno ARM Development Platform SoC.

See the *Juno ARM® Development Platform SoC Technical Reference Manual* for information on the Juno ARM Development Platform SoC.

## 2.3 External power

You supply power to the V2M-Juno motherboard from the mains supply using the on-board connector and an external power supply unit and connector cable that ARM supplies with the board.

The external power supply unit converts mains power to 12V DC that connects to a plug-in ATX power module. The unit accepts mains power in the range 100-240V AC.

Alternatively, you can remove the module and connect an ATX power supply unit directly to the board.

On-board regulators supply power to the V2M-Juno motherboard power domains and to the power domains of the Juno ARM Development Platform SoC.

Power LEDs indicate that power domains are active:

5V 5V domain powered.

3V3 3V3 domain powered

SB\_5V Standby 5V domain powered.

### Related references

1.3 Location of components on the V2M-Juno motherboard on page 1-15. A.1.11 ATX power connector on page Appx-A-129.

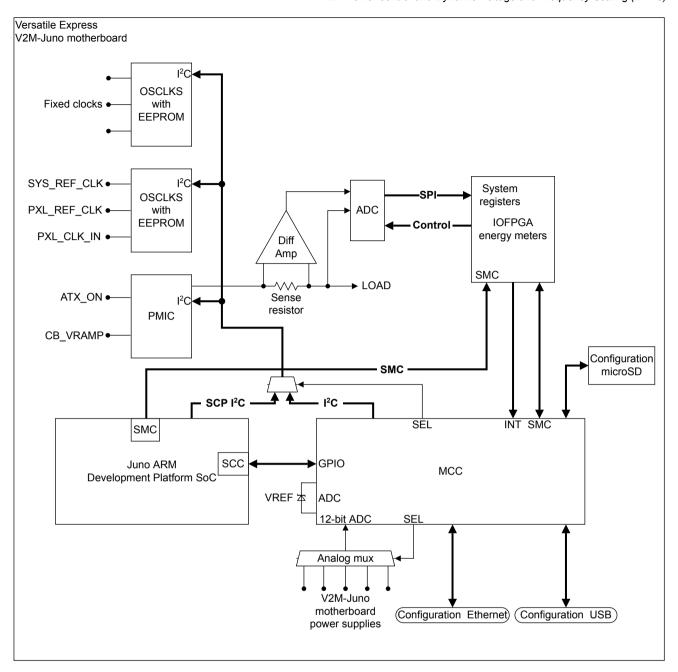

## 2.4 Power control and Dynamic Voltage and Frequency Scaling (DVFS)

DVFS provides voltage, current, and power monitoring.

The V2M-Juno motherboard contains a *Power Management IC* (PMIC) that generates the V2M-Juno motherboard and Juno ARM Development Platform SoC power supplies. The Juno ARM Development Platform SoC, the Juno SoC, configures the PMIC through the System Control Processor (SCP) I<sup>2</sup>C interface during powerup or reset.

| interface during powerup of feset.                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Direct control of the PMIC through the SCP interface during runtime supports voltage scaling.                                                                                                                                            |

| Varying the Juno ARM Development Platform SoC PLL dividers during runtime supports frequency scaling.                                                                                                                                    |

| Note                                                                                                                                                                                                                                     |

| ARM recommends that you use this method to achieve DVFS frequency scaling and do not use external control of the clock generators through the V2M-Juno motherboard SCP I <sup>2</sup> C interface.                                       |

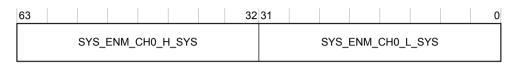

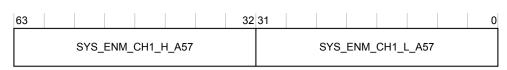

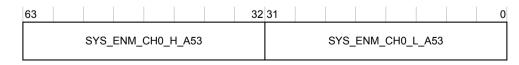

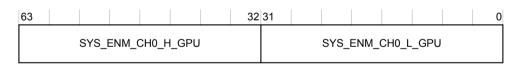

| Dedicated logic blocks in the IOFPGA contain energy meters for the Cortex-A53, Cortex-A57, Mali-T624 GPU and VSYS supplies. The energy meters consist of current, voltage, power and energy registers in the APB Registers memory space. |

| The following figure shows the V2M-Juno motherboard power control and DVFS system.                                                                                                                                                       |

| Note                                                                                                                                                                                                                                     |

| The VSYS supply powers the fabric of the Juno SoC outside the Cortex-A53, Cortex-A57 and Mali-T624 GPU clusters.                                                                                                                         |

|                                                                                                                                                                                                                                          |

Figure 2-3 Power control and DVFS system

See the following documents for more information:

Juno ARM® Development Platform SoC Technical Reference Manual

## **Related concepts**

4.3.1 APB system register summary on page 4-87.

## 2.5 Clocks

This section describes the V2M-Juno motherboard clocks that drive the board, the Juno ARM Development Platform SoC and the LogicTile, if fitted in the daughterboard site. This section contains the following subsections:

- 2.5.1 Overview of clocks on page 2-27.

- 2.5.2 Juno SoC and V2M-Juno motherboard clocks on page 2-28.

- 2.5.3 IOFPGA clocks on page 2-34.

## 2.5.1 Overview of clocks

Clock generators on the V2M-Juno motherboard generate clocks for the internal blocks in the Juno ARM Development Platform SoC, the internal blocks in the IOFPGA, and the peripherals on the board.

During powerup or reset, internal EEPROMs in the clock generators configure the generators to the correct operational clock frequencies. The board.txt file also defines these default clock frequencies. You can change the operational clock frequencies by modifying the configuration board.txt file.

| Note                                |          |               |                |                |     |

|-------------------------------------|----------|---------------|----------------|----------------|-----|

| ARM recommends that you operate the | V2M-Juno | motherboard a | at the default | clock frequenc | ies |

## **Related concepts**

3.3.3 Contents of the MB directory on page 3-70.

2 Hardware Description 2.5 Clocks

## 2.5.2 Juno SoC and V2M-Juno motherboard clocks

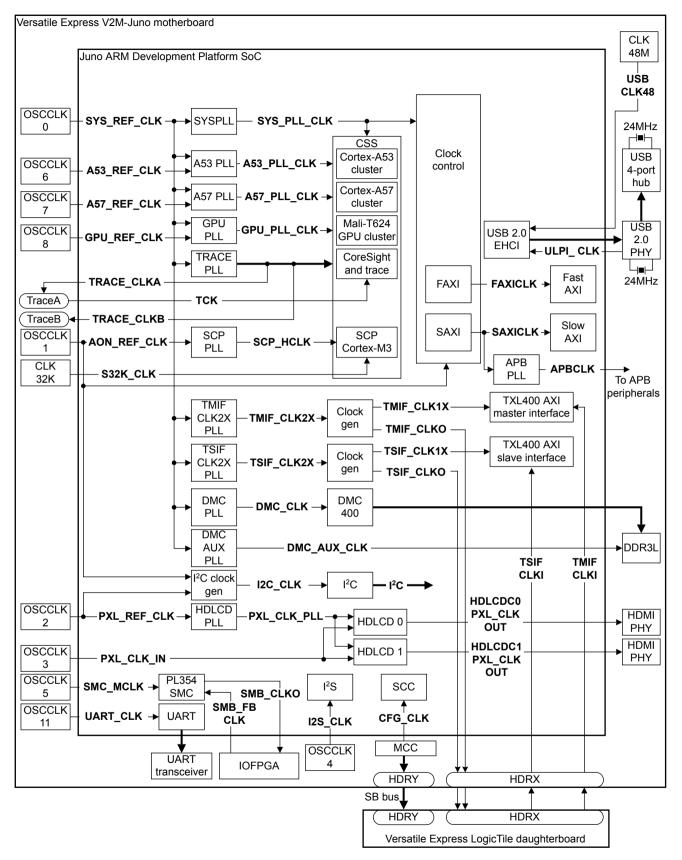

The following figure shows the Juno ARM Development Platform SoC clocks and clock domains. The figure includes the clocks that connect to the LogicTile Express daughterboard, to some of the peripherals on the V2M-Juno motherboard and to the IOFPGA.

Figure 2-4 Juno ARM Development Platform SoC system clocks

The *Compute Subsystem* (CSS) is the subsystem that contains the clusters and System Control Processor (SCP).

The following table shows the internal Juno SoC and V2M-Juno motherboard clocks and their sources.

Table 2-1 Juno SoC clocks and their sources on the V2M-Juno motherboard.

| Juno SoC clock | Source   | Default<br>frequency | Description                                                                                                     |

|----------------|----------|----------------------|-----------------------------------------------------------------------------------------------------------------|

| SYS_REF_CLK    | OSCCLK 0 | 50MHz                | Main system clock for the Juno SoC. Source clock for the following PLLs and clocks inside the Juno SoC:         |

|                |          |                      | SYS_PLL_CLK:  CSS main system clock. 1600MHz.  A57_PLL_CLK:  Cortex-A57 clock. 600MHz-1.2GHz.                   |

|                |          |                      | A53_PLL_CLK:<br>Cortex-A53 clock. 500MHz-1GHz.                                                                  |

|                |          |                      | GPU_PLL_CLK: Mali-T624 GPU clock. 450-900MHz.                                                                   |

|                |          |                      | DMC_CLK: DMC-400 clock. 400MHz.                                                                                 |

|                |          |                      | DMC_AUX_CLK: External DMC interface on V2M-Juno motherboard clock. 800MHz.                                      |

|                |          |                      | FAXICLK: Fast AXI clock. 533MHz.                                                                                |

|                |          |                      | SAXICLK:<br>Slow AXI clock. 400MHz.                                                                             |

|                |          |                      | USBHCLK: Primary clock for the BIU of the USB EHCI and OHCI host controllers. 160MHz.                           |

|                |          |                      | TMIF_CLK2X:  AXI master interface reference clock in the forward direction. 123MHz.                             |

|                |          |                      | TSIF_CLK2X:  AXI slave interface reference clock in the reverse direction. 123MHz.                              |

|                |          |                      | APBCLK: Clocks the SMB_CLK domain in the IOFPGA. 100MHz.                                                        |

|                |          |                      | TRACE_CLKA, TRACE_CLKB: 145.45MHz.                                                                              |

| AON_REF_CLK    | OSCCLK 1 | 50MHz                | Reference clock for the SCP PLL inside the Juno SoC. This derives the following clock:                          |

|                |          |                      | SCPHCLK:  SCP subsystem and AHB expansion area clock.  25MHz-100MHz.Alternative source for FAXICLK and SAXICLK. |

Table 2-1 Juno SoC clocks and their sources on the V2M-Juno motherboard. (continued)

| Juno SoC clock          | Source                     | Default frequency | Description                                                                                                                                 |

|-------------------------|----------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| PXL_CLK_IN              | OSCCLK 3                   | 50MHz             | Default source clock for HDLCD0 and HDLCD1. Used for low resolution displays.                                                               |

| PXL_REF_CLK             | OSCCLK 2                   | 50MHz             | Reference clock for the HDLCD PLL inside the Juno SoC. This generates the following clock:                                                  |

|                         |                            |                   | PXL_CLK_PLL: 25-100MHz. This is the alternative source clock for the HDLCDs.                                                                |

|                         |                            |                   | Note                                                                                                                                        |

|                         |                            |                   | You can independently select  PXL_CLK_PLL as the source clock to  HDLCD0, HDLCD1, or both.                                                  |

| HDLCDC0_PXL_CLK_O<br>UT | HDLCD0 in Juno<br>SoC      | 165MHz            | Pixel clock to HDMI PHY 0 on the V2M-Juno motherboard. The maximum operating frequency of the PHY is 165MHz.                                |

| HDLCDC1_PXL_CLK_O<br>UT | HDLCD1 in Juno<br>SoC      | 165MHz            | Pixel clock to HDMI PHY 1 on the V2M-Juno motherboard. The maximum operating frequency of the PHY is 165MHz.                                |

| A57_REF_CLK             | OSCCLK 7                   | 50MHz             | Alternative reference clock for the A57PLL inside the Juno SoC. This PLL generates the following Cortex-A57 cluster clock:                  |

|                         |                            |                   | A57_PLL_CLK<br>800MHz nominal, 1.1GHz overdrive.                                                                                            |

| A57_REF_CLK             | OSCCLK 7                   | 50MHz             | Alternative reference clock for the A57PLL inside the Juno SoC. This PLL generates the following Cortex-A57 cluster clock:                  |

|                         |                            |                   | A57_PLL_CLK<br>800MHz nominal, 1.1GHz overdrive.                                                                                            |

| A53_REF_CLK             | OSCCLK 6                   | 50MHz             | Alternative reference clock for the A53PLL inside the Juno SoC. This generates the following Cortex-A53 cluster clock:                      |

|                         |                            |                   | A53_PLL_CLK: 700MHz nominal, 850MHz overdrive.                                                                                              |

| GPU_REF_CLK             | OSCCLK 8                   | 50MHz             | Alternative reference clock for the GPUPLL inside the Juno SoC. This derives the following Mali-T624 GPU cluster-specific clock:            |

|                         |                            |                   | GPU_PLL_CLK: 600MHz nominal. No overdrive.                                                                                                  |

| S32K_CLK                | CLK_32K clock<br>generator | 32.768kHz         | Fixed frequency real-time clock. Provides a real-time private time domain for the SCP that uses it to implement very low-power sleep modes. |

Table 2-1 Juno SoC clocks and their sources on the V2M-Juno motherboard. (continued)

| Juno SoC clock | Source                                                                                               | Default frequency | Description                                                                                                                      |

|----------------|------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|

| I2S_CLK        | OSCCLK 4                                                                                             | 75MHz             | Integrated-IC sound clock. Clocks the I <sup>2</sup> S audio bus.                                                                |

| I2C_CLK        | OSCCLK 1 or<br>OSCLK 2                                                                               | 50MHz             | Clocks the I <sup>2</sup> C control bus.  —— Note ——  The default input to the I <sup>2</sup> C clock generator is               |

|                |                                                                                                      |                   | OSCCLK 1.                                                                                                                        |

| UART_CLK       | OSCCLK 11                                                                                            | 7.2738MHz         | Clocks the UART interface.                                                                                                       |

| TCK            | Trace connector                                                                                      | 25MHz             | From external trace port analyzer. Clocks the Trace debug system.                                                                |

| ULPI_CLK       | USB2 2.0 xtal clock generator.                                                                       | 60MHz             | Fixed frequency clock. Clocks the <i>USB 2.0 Transceiver Macrocell Interface Low-Pin Interface</i> (ULPI) from the off-chip PHY. |

| USB_CLK48      | CLK_48M clock generator.                                                                             | 48MHz             | Primary clock input to the USB controller.                                                                                       |

| SMC_MCLK       | OSCLK 5                                                                                              | 50MHz             | Clocks the PL354 <i>Static Memory Controller</i> (SMC) interface.                                                                |

| SMB_FB_CLK     | IOFPGA                                                                                               | 50MHz             | Feedback clock from IOFPGA to read data back into PL354 in synchronous mode. SMC uses this to adjust timing.                     |

| SMB_CLKO       | OSCLK 5                                                                                              | 50MHz             | Derived from <b>SMC_MCLK</b> . Exported out of Juno SoC to SMB timing adjust block in IOFPGA.                                    |

| CFG_CLK        | MCC.                                                                                                 | 10MHz             | Serial Configuration Controller (SCC) serial interface clock.                                                                    |

| TMIF_CLKI      | TLX400 Thin Links<br>AXI slave interface<br>in FPGA on<br>LogicTile fitted in<br>daughterboard site. | 61.5MHz           | Clock in the receive direction to the TLX400 Thin Links AXI master interface on the Juno SoC.                                    |

| TMIF_CLKO      | TLX400 Thin Links<br>AXI master interface<br>reference clock<br>generator in Juno<br>SoC.            | 61.5MHz           | Clock in the transmit direction from the TLX400 Thin Links AXI master interface on the Juno SoC.                                 |

Table 2-1 Juno SoC clocks and their sources on the V2M-Juno motherboard. (continued)

| Juno SoC clock | Source                                                                                                | Default<br>frequency | Description                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------|

| TSIF_CLKI      | TLX400 Thin Links<br>AXI master interface<br>in FPGA on<br>LogicTile fitted in<br>daughterboard site. | 0 - 10 - 1 - 1 - 1   | Clock in the receive direction to the TLX400 Thin Links AXI slave interface on the Juno SoC.    |

| TSIF_CLKO      | TLX400 Thin Links<br>AXI slave interface<br>reference clock<br>generator in Juno<br>SoC.              | 61.5MHz              | Clock in the transmit direction from the TLX400 Thin Links AXI slave interface on the Juno SoC. |

The MCC uses the board.txt configuration file in the microSD card to set the frequency of the board clock generators. You can adjust these default clock frequencies by editing this file. You can also adjust the board clocks during runtime by using the SYS\_CFG register interface.

The Juno SoC has internal PLLs and clock generators that generate clocks to drive the Juno SoC internal systems.

See the *Juno ARM® Development Platform SoC Technical Reference Manual* for more information on the following:

- The Juno SoC internal clocks and their default values.

- Selecting alternative source clocks.

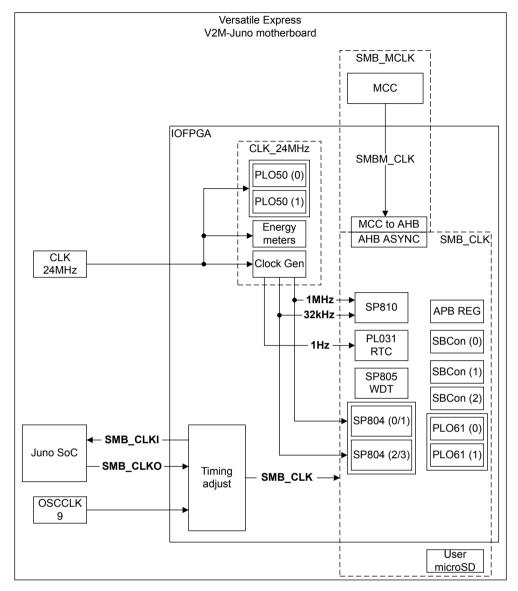

## 2.5.3 IOFPGA clocks

The following figure shows the IOFPFA clocks and clock domains.

Figure 2-5 IOFPGA clocks

The bootup clock for the peripherals in the *SMB\_CLK* domain during powerup and configuration is *OSCCLK 9* on the V2M-Juno motherboard. The clock source then switches to **SMB\_CLKO** from the Juno SoC that becomes the master clock for the *SMB\_CLK* domain during runtime.

2 Hardware Description 2.5 Clocks

Table 2-2 V2M-Juno motherboard OSCCLK clock sources

| Clock name | Source                                                             | Default<br>Frequency  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|--------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMB_CLK    | OSCCLK 9 during powerup and configuration  SMB_CLKO during runtime | 50MHz                 | Reference clock for the <i>SMB_CLK</i> domain. This domain contains the following IOFPGA peripherals and subsystems:                                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |                                                                    |                       | <ul> <li>AHB subsystem.</li> <li>APB subsystem.</li> <li>PL031 Real-Time Clock.</li> <li>APB system registers.</li> <li>System Bus Controllers (SBCon).</li> <li>SP805 Watchdog Timer.</li> <li>SP804 Dual-Timers.</li> <li>PL061 GPIO.</li> <li>SP810 System Controller.</li> </ul>                                                                                                                                                                                                                                                        |

| CLK_24MHZ  | CLK_24MHZ clock generator.                                         | 24MHz fixed frequency | Reference clock for the following blocks inside the SMB_CLK clock domain:  • PL050 Keyboard and mouse interfaces.  • Energy meters, that is the voltage, current, power and accumulated energy meters.  • The clock generator that generates the source clocks 32kHz and 1MHz for the SP810 System controller and the 1Hz clock for the PL031 Real-Time Clock.  — Note — Note — The SP810 System Controller selects 32kHz or 1MHz as the clock source for the SP805 and the SP804 blocks.  — The frequency of the clock 32kHz is 32.768kHz. |

| SMB_MCLK   | MCC                                                                | 50MHz                 | Master clock for the SMB_MCLK domain. The SMB_MCLK domain includes the MCC and the MCC to AHB fabric in the IOFPGA.                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 2.6 Resets

This section describes the reset push buttons, the reset architecture, and the reset timing sequence.

This section contains the following subsections:

- 2.6.1 Reset push buttons on page 2-36.

- 2.6.2 Reset architecture on page 2-36.

- 2.6.3 Reset sequence on page 2-38.

## 2.6.1 Reset push buttons

The V2M-Juno motherboard provides two reset push buttons.

## Hardware Reset push button

| • | Pressing the <i>Hardware Reset</i> button during runtime generates <b>nPBRESET</b> , performs a hardware |

|---|----------------------------------------------------------------------------------------------------------|

|   | reset and puts the system into standby state.                                                            |

|   |                                                                                                          |

| The second secon |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| The $Hardware\ Reset$ push button is the black push button. The V2M-Juno motherboard labels it as $nPBRESET$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## ON/OFF/Soft Reset push button

- Pressing the *ON/OFF/Soft Reset* button briefly during runtime performs a software reset of the system.

- Pressing the *ON/OFF/Soft Reset* for more than two seconds puts the system into the standby state in the same way as pressing the *Hardware Reset* button.

| Note                                                                            |                                       |

|---------------------------------------------------------------------------------|---------------------------------------|

| The <i>ON/OFF/Soft Reset</i> push button is the red push button. <i>nPBON</i> . | The V2M-Juno motherboard labels it as |

## **Related concepts**

3.5.1 ON/OFF/Soft Reset button on page 3-75. 3.5.2 Hardware Reset button on page 3-75.

## Related references

1.3 Location of components on the V2M-Juno motherboard on page 1-15.

## 2.6.2 Reset architecture

The following figure shows an overview of the V2M-Juno motherboard reset system.

Figure 2-6 V2M-Juno motherboard resets

## CB\_nPOR

This is the main powerup reset for the Juno ARM Development Platform SoC, and the devices and peripherals on the V2M-Juno motherboard including the IOFPGA. Signal **CB\_nPOR** drives signal **nPORESET** inside the Juno ARM Development Platform SoC.

### nTRST

This resets the CoreSight DAP and the TAP controllers inside theJuno SoC.

## CFG\_nRST

This is the reset signals for the serial interface to the SCC registers in the Juno ARM Development Platform SoC. It resets the SCC registers to their default values. It also resets the IOFPGA peripherals and the clock generators on the V2M-Juno motherboard.

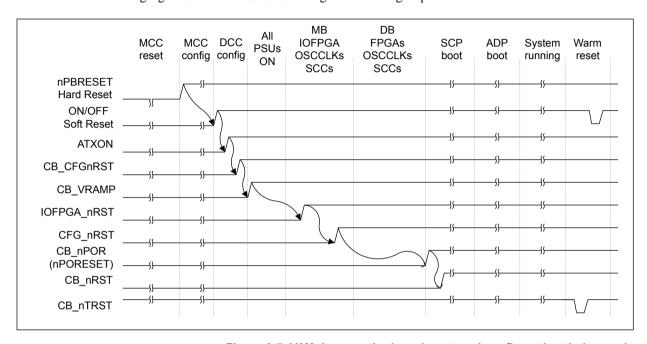

### 2.6.3 Reset sequence

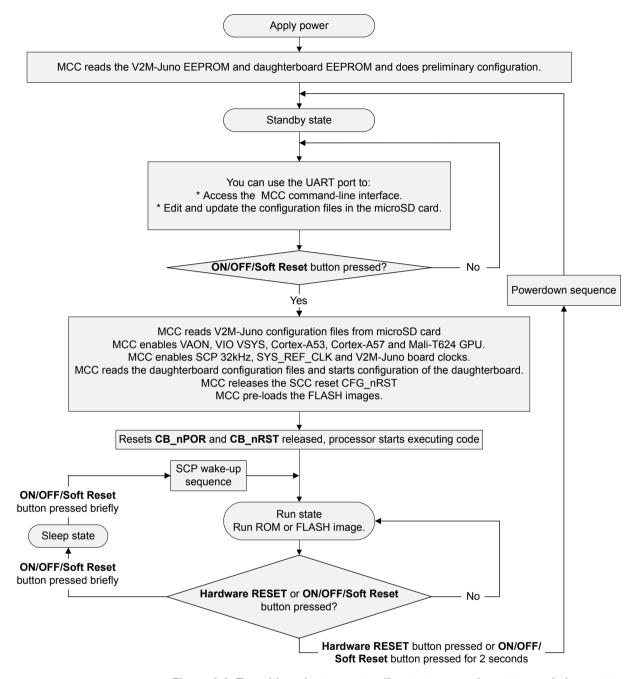

The following figure shows the reset and configuration timing sequence.

Figure 2-7 V2M-Juno motherboard reset and configuration timing cycle

### 2.7 Thin Links AXI master and slave interfaces

The Juno ARM Development Platform SoC contains one AXI master interface and one slave AXI interface that connect to the FPGA in the LogicTile Express daughterboard. A Thin Links TLX-400 interface compresses the AXI master and slave interfaces to reduce the pin count.

The width of the TLX-400 slave interface on the Juno ARM Development Platform SoC is greater than the width of the master interface.

The default Thin Links clock frequency of 61.5MHz gives the following operating speeds:

- Juno SoC master interface:

- Forward direction, that is, from the Juno SoC to the FPGA: 68Mbps.

- Reverse direction, that is, from the FPGA to the Juno SoC: 78Mbps.

- Juno SoC slave interface:

clocks to 61.5MHz.

- Forward direction, that is, from FPGA to Juno SoC: 246Mbps.

- Reverse direction, that is, from Juno SoC to FPGA: 305Mbps.

| Note                                                                                                    |

|---------------------------------------------------------------------------------------------------------|

| ARM recommends that you operate the Thin Links interfaces at the default speeds. See 3.3.4 Contents of  |

| the SITE 1 directory on page 3-71 for an example hoard, tyt configuration file that sets the Thin Links |

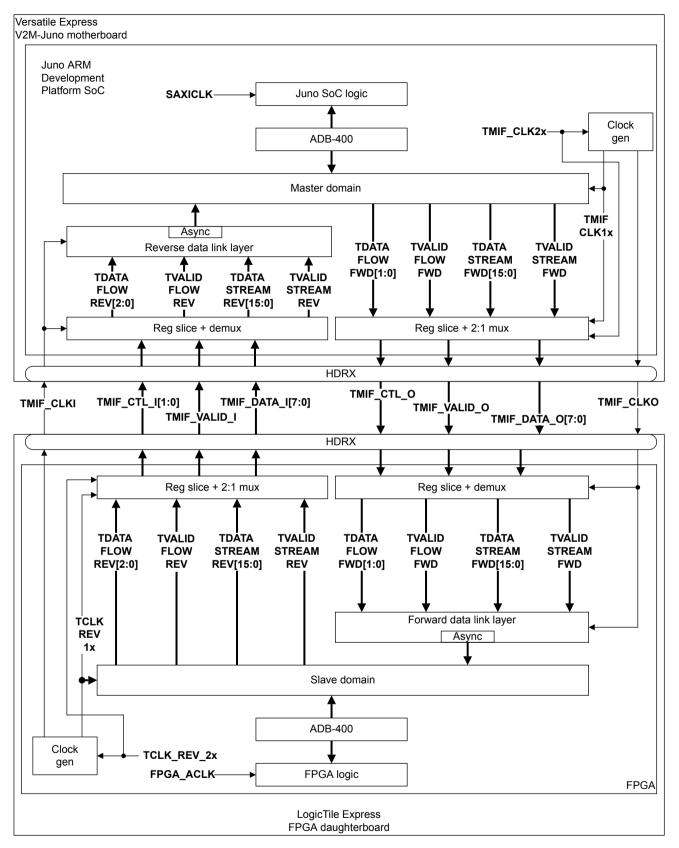

The following figure shows the Thin Links TXL-400 master interface on the Juno ARM Development Platform SoC and its connection to the Think Links TXL-400 slave interface on the LogicTile Express daughterboard.

Figure 2-8 Thin Links AXI master interface

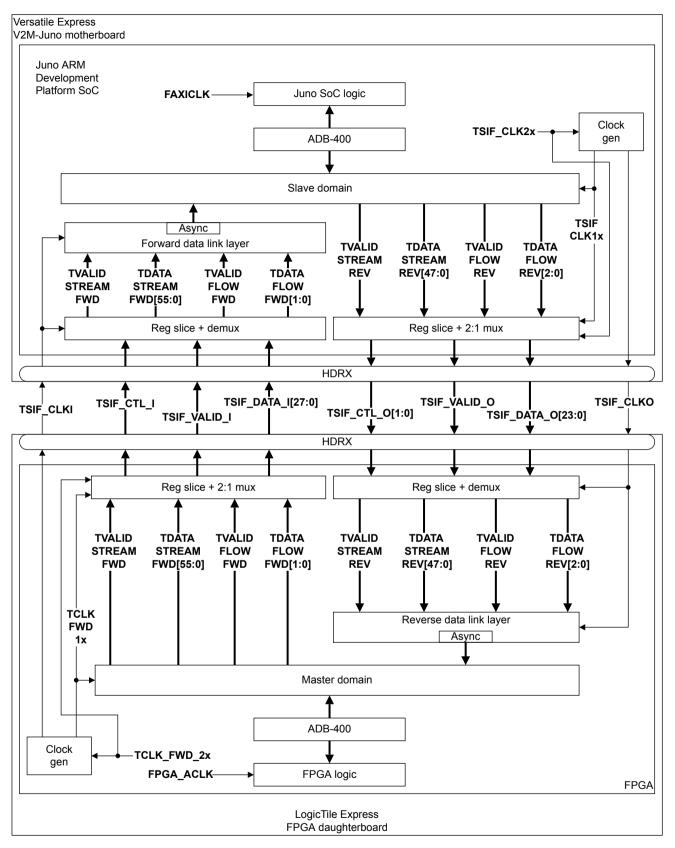

The following figure shows the Thin Links TXL-400 slave interface on the Juno ARM Development Platform SoC and its connection to the Think Links TXL-400 master interface on the LogicTile daughterboard.

Figure 2-9 Thin Links AXI slave interface

2 Hardware Description 2.8 IOFPGA

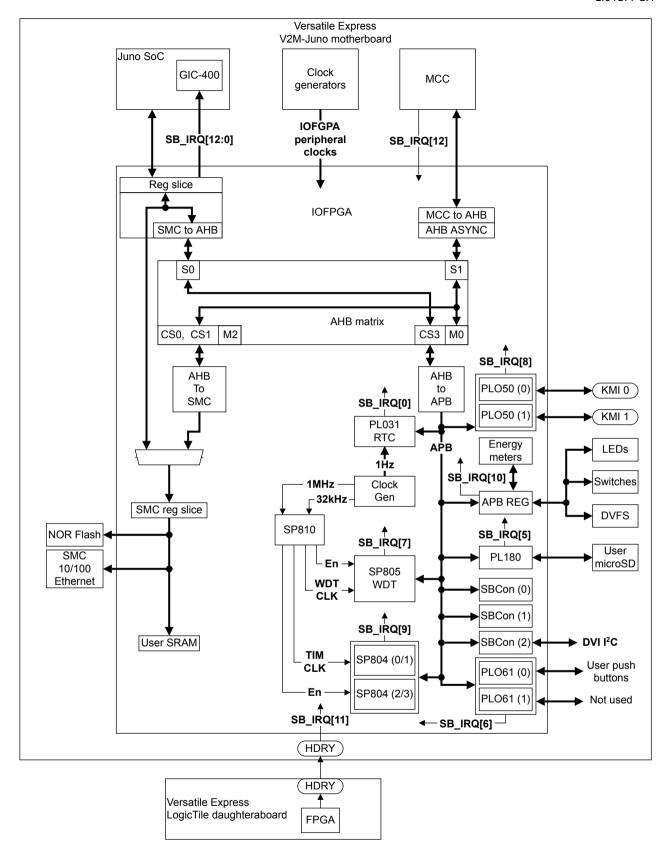

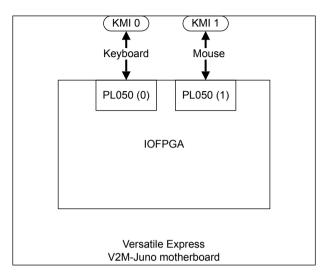

## 2.8 IOFPGA

The IOFPGA provides access to low bandwidth peripherals that the Juno ARM Development Platform SoC does not provide. The Juno ARM Development Platform SoC provides access to the IOFPGA through an SMC interface.

The following figure shows the internal architecture of the IOFPGA and its connectivity to external peripherals, including the external interrupts to the GIC-400 interrupt controller in the Juno ARM Development Platform SoC.

Figure 2-10 IOFPGA internal architecture

The following table shows the peripherals and buses inside the IOFPGA.

| Peripheral   | Interface or application                                       | Release version                              |

|--------------|----------------------------------------------------------------|----------------------------------------------|

| PL031        | RTC.                                                           | r1p0.                                        |

| PL050        | Keyboard and mouse interfaces.                                 | r1p0.                                        |

| PL061        | GPIO for additional user key entry and trusted keyboard entry. | r1p0.                                        |

| SP804        | Dual-timer.                                                    | r1p2.                                        |

| SP805        | Watchdog Timer.                                                | r2p0.                                        |

| PL350 Series | SMC Controller.                                                | r1p0.                                        |

| AHB bus      | -                                                              | AMBA 3 AHB-Lite Protocol Specification v1.0. |

| APB bus      | -                                                              | AMBA 3 APB Protocol Specification v1.0.      |

| Note |  |

|------|--|

|      |  |

The peripheral versions apply to the Revision B V2M-Juno motherboard.

# **Related concepts**

4.2.2 IOFPGA system peripherals memory map on page 4-83.

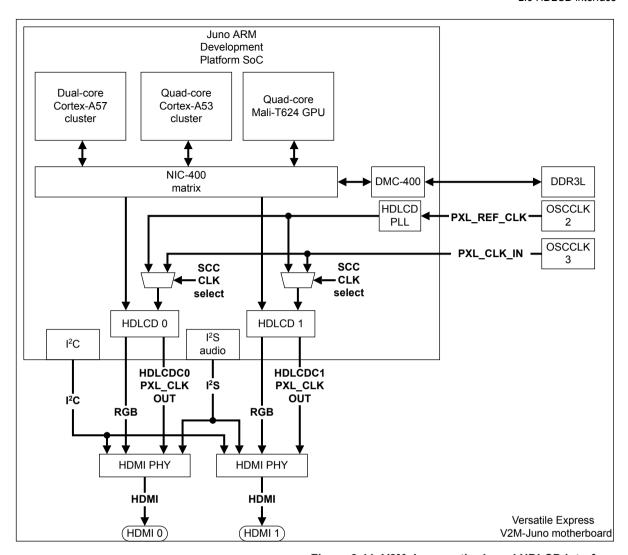

## 2.9 HDLCD interface

Two HDMI PHYs on the V2M-Juno motherboard provide video graphics.

Two HDLCD controllers in the Juno ARM Development Platform SoC support all common 24-bit RGB formats. These are simple frame buffers whose RGB video connects to IO drivers that drive the PHYs. The PHYS can operate at a maximum pixel clock frequency of 165MHz. This interface supports HDMI 1.4a up to 1080p.

There are two clock sources for the pixel clocks on the V2M-Juno motherboard:

- OSCCLK 2 is the source clock for HDLCD PLL that generates PXL CLK PLL.

- OSCCLK 3 is the source clock for PXL CLK IN.

| Note                                                                                |                                              |

|-------------------------------------------------------------------------------------|----------------------------------------------|

| You can independently select <b>PXL_CLK_IN</b> or <b>PX</b> for HDLCD 0 or HDLCD 1. | L_CLK_PLL during runtime as the clock source |

A typical use of HDLCD0 is for lower resolution video than HDLCD1 and to be clocked directly from **PXL\_CLK\_IN** without using the PLL.

The HDLCD 24-bit data connects directly between the Juno ARM Development Platform SoC and the HDMI controllers on the V2M-Juno motherboard. The HDMI controllers drive the HDMI connectors. The Juno ARM Development Platform SoC configures the HDMI controllers at powerup or reset over the AP I<sup>2</sup>C bus.

The HDMI controllers support I<sup>2</sup>S audio from the Juno ARM Development Platform SoC. They drive the audio to the HDMI connectors. The same audio stream connects to both HDMI connectors.

| Note                                                                                                                                                      |              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Software that ARM supplies with the V2M-Juno motherboard configures the Juno SoC enable correct operation of the HDLCD interface and correct HDMI output. | and board to |

The following figure shows the HDLCD video system on the V2M-Juno motherboard.

Figure 2-11 V2M-Juno motherboard HDLCD interface

The default clock for the HDLCD controllers is **PXL\_CLK\_IN**. See the Juno ARM Development Platform SoC Technical Reference Manual for information on the following:

- The Juno SoC internal clocks and their default values.

- Selecting alternative source clocks.

### Related references

A.1.8 HDMI connectors on page Appx-A-125.

1.3 Location of components on the V2M-Juno motherboard on page 1-15.

# 2.10 Interrupts

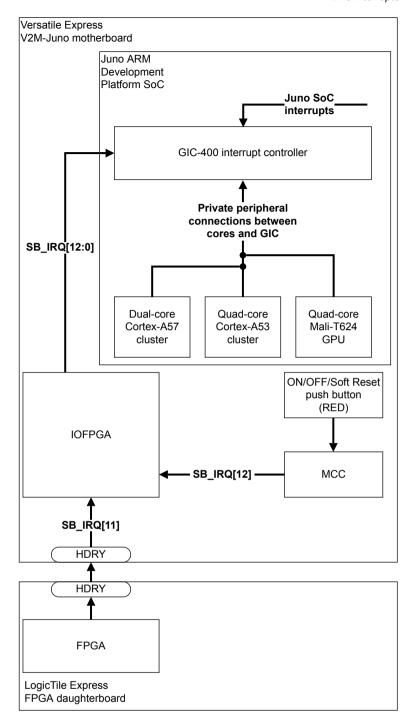

The Juno ARM Development Platform SoC implements a GIC-400 generic interrupt controller with 13 external interrupts.

Seven of the external interrupts connect to IOFPGA peripherals, one connects to the SMC 10/100 Ethernet, one connects to the MCC, and one connects to the LogicTile daughterboard site. The other three external interrupts are reserved.

—— **Note**The prototype board provides an SMC USB 2.0 interface that the production board does not provide. The SMC USB 2.0 uses one of the reserved interrupts leaving two external interrupts as reserved on the prototype board.

The MCC generates its interrupt when you press the *ON/OFF/Soft Reset* push button. All interrupts connect to the GIC-400 interrupt controller in the Juno ARM Development Platform SoC through the IOFPGA.

The following figure shows an overview of the external interrupt signals from the V2M-Juno motherboard peripherals to the GIC-400 interrupt controller in the Juno ARM Development Platform SoC.

Figure 2-12 Juno ARM Development Platform SoC interrupts overview

The following table shows the mapping of the external interrupt signals to the GIC-400 controller in the Juno ARM Development Platform SoC. It lists the sources of the interrupts that originate in the V2M-Juno motherboard or the LogicTile Express fitted in the daughterboard site.

Table 2-3 External interrupt signals to V2M-Juno Arm Development Platform

| Interrupt ID | GIC IRQ ID | Motherboard signal name | Source                                                                        |  |

|--------------|------------|-------------------------|-------------------------------------------------------------------------------|--|

| 99-96        | 67-64      | -                       | Juno ARM Development Platform SoC internal peripherals and systems.           |  |

| 100          | 68         | SB_IRQ[0]               | IOFPGA-PL031 RTC.                                                             |  |

| 102-101      | 70-69      | SB_IRQ[2:1]             | IOFPGA-Reserved interrupts.                                                   |  |

| 191-103      | 159-71     | -                       | Juno ARM Development Platform SoC internal peripherals and systems.           |  |

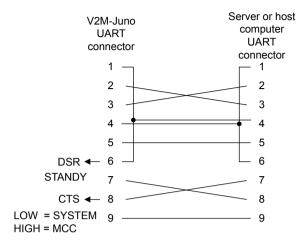

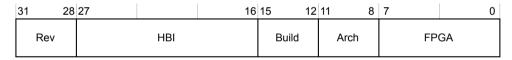

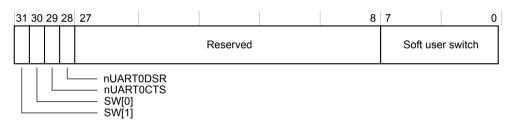

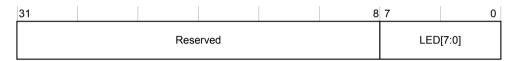

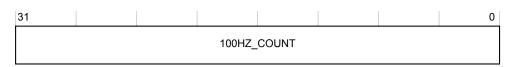

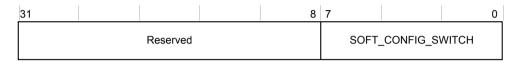

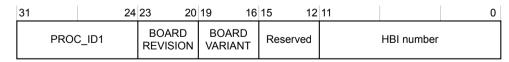

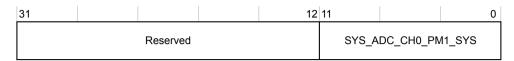

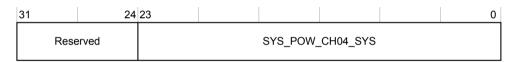

| 192          | 160        | SB_IRQ[3]               | IOFPGA-SMC 10/100 Ethernet.                                                   |  |