Traffic Mixes in Networking Infrastructure - Base Transceiver Station (BTS) with CCN Interconnects

IntroductionARM recently announced the next in the family of CCN (Cache Coherent Network) solutions. Specifically we introduced the CoreLink CCN-508. A quick recap – CoreLink CCN-508 is a cache coherent network providing support for up to 32 fu...

By Ian Forsyth

Introduction

ARM recently announced the next in the family of CCN (Cache Coherent Network) solutions. Specifically we introduced the CoreLink CCN-508. A quick recap – CoreLink CCN-508 is a cache coherent network providing support for up to 32 fully coherent cores. It has an integrated snoop filter and a configurable integrated L3 cache, 24 ports of AMBA 4 AXI4/ACE-Lite interfaces useful in IO coherent heterogeneous processing, hardware acceleration and high speed I/O. It also supports high memory bandwidth with up to four x72 channels of DDR.

CoreLink CCN-508 interconnect can scale to different networking solutions which have different traffic profiles by incorporating different combinations of CPU, GPU, DSP, and Accelerators.

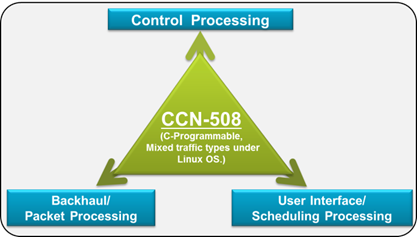

Interconnect by definition - is to be joined to something else or to a number of joined things, or make something part of such a network and the CoreLink CCN family is found in the center of control processing, backhaul, packet processing, user interfacing and scheduling processing solutions, see Figure 1.

Figure 1 Applicability of the CoreLink CCN-508

Figure 1 Applicability of the CoreLink CCN-508

Networking Use-case: BTS

A base transceiver station (BTS) is a piece of equipment that facilitates wireless communication between user equipment (UE) and a network. UEs are devices like mobile phones and tablets with wireless Internet connectivity. The network can be that of any of the wireless communication technologies like GSM, CDMA, wireless local loop, Wi-Fi, WiMAX or other wide area network (WAN) technology. BTS is also referred to as the radio base station (RBS), node B (in 3G Networks) or, simply, the base station (BS).

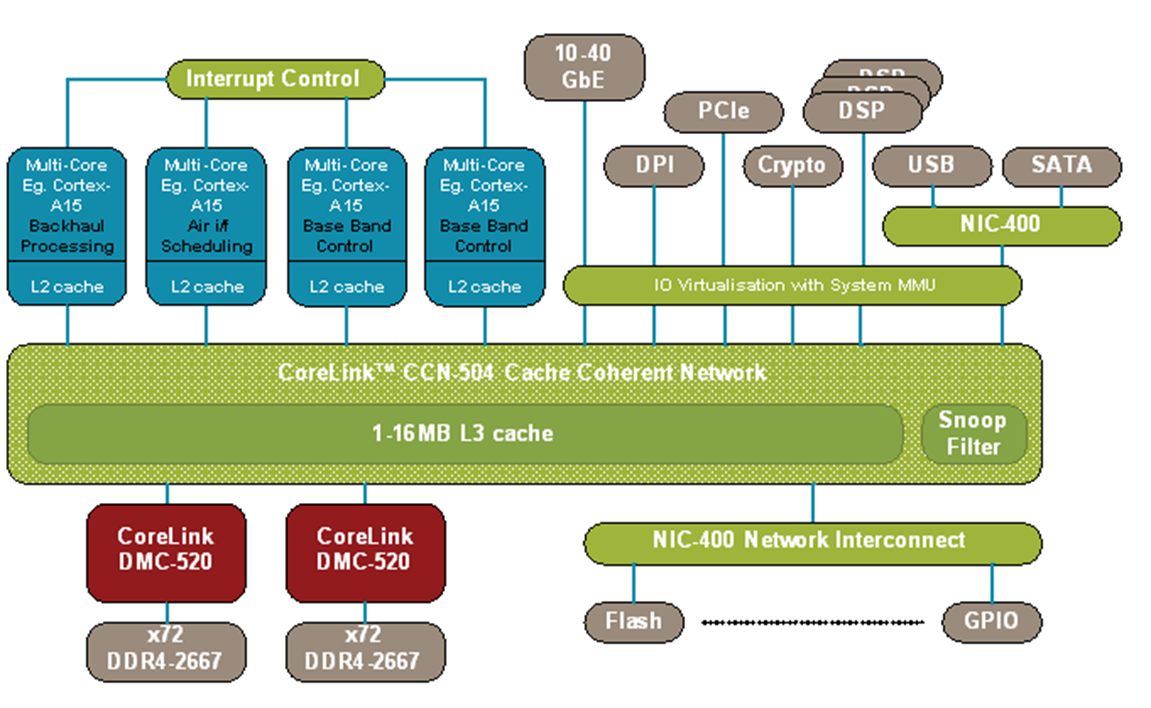

The BTS application typically uses many-core processing for thread-able workloads. An example ARM based SOC utilizes CoreLink CCN interconnect products with a mix of Cortex-A CPU cores, memory controllers and acceleration engines. The point of coherency is managed by the L3 in the interconnect. Figure 2 shows a Macro base station platform that could be used in 2G, 3G, and 4G infrastructure platforms.

Figure 2 Macro Cell BTS Base Band Unit

Here one cluster is used for backhaul processing, another for air interfacing scheduling and remaining two for baseband control. The performance of the coherent interconnect (in this case the CCN-504) is deterministic and consistent across different implementations. This allows system developers to predict performance and scale solutions from a small number of cores to many cores.

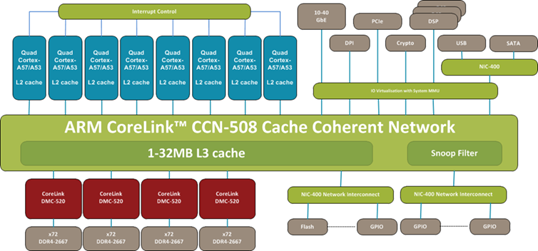

Essentially you can scale the numbers of cores and the performance according to Base Band Unit need (control, packet processing offload and air interface scheduling). The CoreLink CCN-508 doubles the maximum core count to 32 fully cache coherent ARM cores, compared with a maximum of 16 cores with the CoreLink CCN-504.

Figure 3 Macro Cell BTS Base Band Unit with enhanced compute performance

Figure 3 Macro Cell BTS Base Band Unit with enhanced compute performance

Macro BTS capability (L3, L2, L1, transport and security) can be supplemented with large-scale computing workloads on near-infinite virtual machines in the SOC. Virtualization extensions supported in the cores and the interconnect can be used to virtualize storage and I/O functions.

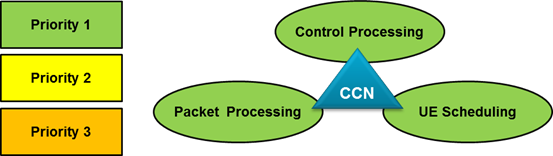

Figure 4 BTS Application has Control and Packet processing and UW scheduling as top priorities

Figure 4 shows the interrelationship between control processing, packet processing and UE scheduling - all are important priorities in these types of applications.

Possible Future

Network traffic is exploding within the Data Center so in Figure 3, I am suggesting that it is possible to scale the processing capability by adding more cores to the coherent interconnect. The CCN family continues to expand up and down to scale current and new solutions. In the future it may be possible to integrate the high performance server capability into these Macro BTS Base Band unit designs.

Let’s wait and see….

If you want to hear more about this exciting technology join us at ARM Techcon session ATC-222 on Wednesday October 30th at 2:30pm. Direct Link

By Ian Forsyth

Re-use is only permitted for informational and non-commerical or personal use only.